時域反射儀的硬件設計與實現----關鍵電路設計(五)

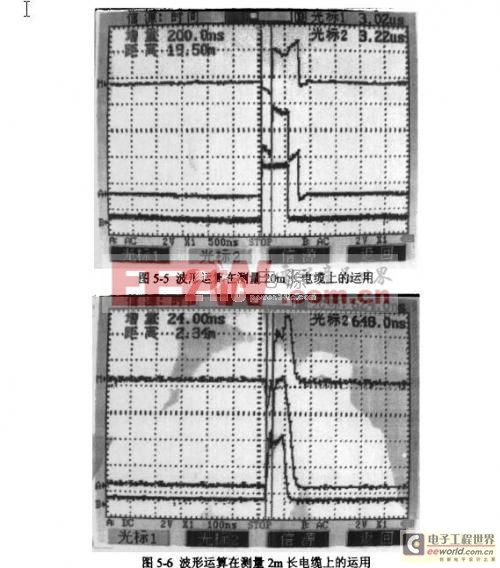

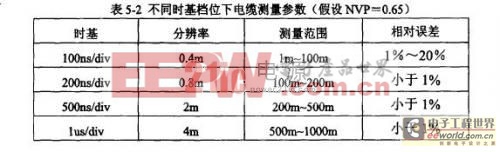

從上面兩個測量波形可以看出,利用波形運算的方法,可以消除一定的測量盲區。在測量短距離情況下,如果用較窄的測量脈沖,屏幕上顯示的波形前沿不夠好。通過增加測量脈沖信號的寬度以后,再利用波形減法運算,可以得到比較好的測試結果,同時使測量盲區保持在lm以內。圖5-6的測量結果顯示,在短距離測量情況,測量誤差比較明顯。因為在該時基狀態下的分辨率為0.4m,為實際長度的20%,由于分辨率相對于2m的電纜來說已經比較大了,所以導致測量的不準確,同時儀器本身還引入了一定的系統誤差,實際測量誤差為0.34m,相對誤差為17%.如果采用更小檔位的時基,測量結果應該更加準確。但由于在更小檔位下,屏幕上顯示的波形因順序等效采樣的不理想,導致顯示出的波形較難分辨出脈沖前沿,因此在這里沒有給出。表5-2給出來不同時基檔位下進行電纜測量的相關參數。

4.2 結論

經過對本設計硬件部分的分析論證和設計,以及在后期的不斷的電路調試和方案修改,基本上完成了本文的設計任務。

本設計以傳輸線傳輸理論為基礎,利用脈沖反射的原理,完成了時域反射儀的整體的硬件部分的設計。通過論文工作,作者基本完成了以下內容:

1.利用FPGA內部數字邏輯單元完成了寬度可變的脈沖信號,同時利用了游標卡尺原理在FPGA完成了脈沖信號的等效延時模塊設計,實現了脈沖信號的高速等效采樣。

2.將由數字電路產生的脈沖信號做放大處理,并利用功率分配電路將測試脈沖送到測試端。

3.脈沖信號的調理模擬通道的設計,包括粗衰減、阻抗變換、可變增益放大電路,調整垂直偏移電路、通道前端串轉并控制電路。

4.高速數據采集和存儲部分電路設計,包括數據高速采集電路、峰值檢測模塊、預觸發模塊。

5.手持式設備電源部分設計:鏗電池充電管理電路設計、利用DC/DC變換器將電池電壓轉換成系統所需要的各種直流電壓,防反跳開關控制器電路設計。

6.其它本文沒有介紹的部分,如真有效值萬用表電路的設計,鍵盤電路,具有光電隔離RS232轉USB接口電路設計,CPLD驅動液晶顯示部分設計,涉及到顯示數據的存儲、調出和修改等。

在本課題的研究和設計基本上完成了預定目標,但通過最終的測試和驗證,發現還有許多問題需要進一步改進和解決。

評論