時域反射儀的硬件設計與實現----關鍵電路設計(一)

3.1低壓窄脈沖源設計

脈沖信號源的整體設計包括脈沖信號的產生模塊設計、脈沖信號等效延時模塊設計,脈沖信號放大、發送模塊的設計。

3.1.1脈沖信號產生

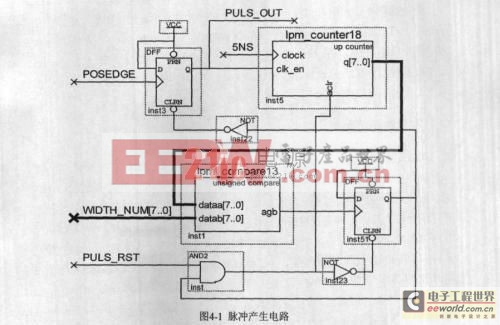

脈沖的寬度通過計數器的方式來進行控制,一個上升沿啟動一個D觸發器產生一個從低到高的電平變化,該電平變化作為脈沖的上升沿,同時用該高電平啟動一個計數器計數,計數時鐘的周期為Δt。計數值輸出端作為一個比較器的一個輸入,比較器的另一個輸入端被預置一個計數次數N,N的大小決定脈沖寬度,當計數器的輸出與N值相同時,比較器輸出一個狀態信號將D觸發器清零,此時一個脈寬為N*Δt的脈沖信號已經產生。如圖4一1所示。

從脈沖產生電路可知,POSEDGE信號通過D觸發器產生脈沖信號的前沿,同時該前沿使能一個8位寬度的二進制計數器,計數器的輸出與預設寬度數值做比 較,當達到預設寬度時,比較器輸出端產生的上升沿信號觸發另一個D觸發器產生一個高電平信號(脈沖狀態信號),該高電平信號將前面的D觸發器清零,即輸出 了脈沖信號的下降沿。PULs一ST是一個復位信號,高電平有效,即在產生脈沖以后需要將計數器和狀態信號清掉,以便為下次脈沖產生做準備。可以看到,復位信號必須要和第2個D觸發器的輸出端進行相與后才能工作,也就是說復位信號必須在脈沖完成之后才有效。

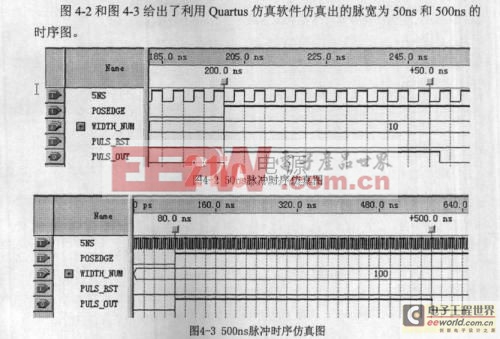

從上面兩個仿真圖可以觀察出,產生出來的脈沖寬度都超過了設定值,產生了誤差,可以看到誤差,主要是因為在POSEDGE信號上升沿時,計數脈沖信號過了半個周期才到,因此該誤差剛好為半個周期計數脈沖的時間,即為2.5ns,該誤差就是我們常說的±1誤差。在實際測量中,脈沖信號的前沿是最關心的部分,因此寬度的不準確性對于測量不會造成影響。

3.1.2脈沖信號延時

前面已經討論過,在時基為100ns/div時,剛好達到ADC的最大采樣極限(250MsPs),當時基進入更快檔位時,如果要進行正常的顯示就需要更多的數據。通過兩種辦法可以實現:軟件插值和等效采樣。采用軟件插值的方式會導致脈沖信號沿失真,影響測量準確度,在這里采用順序時間等效采樣,即將采樣信號與脈沖信號做相對延時,相對延時的時間△t越小,等效采樣率越大,經過多次采樣后,得到顯示所需要的數據。為了保證波形刷新率,等效采樣率隨時基可變,即時基不同時,相對延時的時間△t也不同。與此同時,在進行順序等效的時候,時基越小,需要的等效延時的次數越多,即顯示單次波形需要采樣的次數越多。

表4一1給出了在不同時基情況下的相對延時的時間△t、采樣次數和等效采樣率。

評論