基于DDS與USB技術的通信對抗教學演示系統中硬件的設計與實現

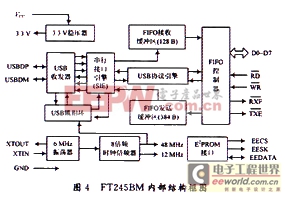

在控制模塊中LISB芯片選用的是FTDI公司的FT245BM。該芯片是FTDI公司早期生產的一種較通用的支持USB 1.1標準的專用芯片,其優點在于芯片通用性好,無需固件配置,控制時序簡單,而且廠家提供了完備的各類庫函數供編程使用,極大地縮短了開發周期。

FT245BM內部結構框圖如圖4所示,FT245BM內部主要由USB收發器、串行接口引擎(SIE)、USB協議引擎和先進先出(FIFO)控制器等構成。他的一個比較明顯的優點就是,內部集成的模塊功能完備,不需要在使用時重新對其進行配置。在接收到主機發出的控制命令后,USB收發器自動執行命令,并通過串行接口引擎完成USB數據的串/并雙向轉換。USB協議引擎按照USB 1.1的規范來完成對FIFO控制器的管理,FIFO控制器通過其兩個握手信號的輸出端口RXF#和TXE#來引導外部主控制器對USB芯片的讀寫控制。

4系統的設計實現

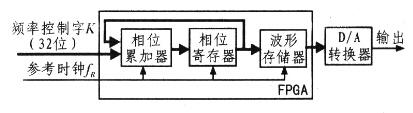

4.1 干擾模塊的設計

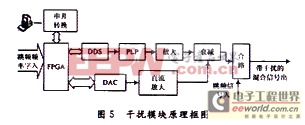

干擾模塊原理圖如圖5所示。在干擾模塊的設計中,選用了常用的DDS芯片AD9854與FPGA相結合的方式來產生干擾頻率。為了實現干擾信號功率的可控制,擬在DDS輸出的信號加上衰減器。采用計算機通過USB芯片來控制干擾模式的選擇和干擾信號參數的選擇。DDS產生的信號先通過低通濾波再放大,目的是為抑制雜散信號。

在跟蹤式干擾中,FPGA接收電子偵察所獲得的通信信號,引導DDS產生同頻的干擾信號。在非跟蹤式干擾中,由計算機控制產生單頻干擾、掃頻干擾以及隨機調頻噪聲等樣式的干擾信號,這些干擾信號和原跳頻信號在合路器合路輸出,送給跳頻接收機,以此來檢驗跳頻通信對這些干擾樣式的抗干擾能力。

4.2控制模塊的設計

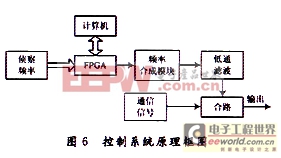

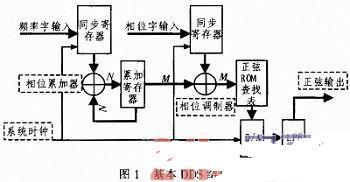

在系統的整體設計過程中,非常重要的部分就是對于整個實驗系統的控制。系統的整體控制模塊原理框圖如圖6所示。

從圖中可以看出,干擾模塊中的FPGA芯片,在系統控制中起著核心作用。在該模塊中,FPGA主要完成4個方面的任務:

(1)實現與電子偵察模塊的實時通信,不斷地接收偵察模塊送來的跳頻信號信息,并立即做出相應的反應。

(2)實現與計算機主機的通信,控制USB芯片的讀寫程序,隨時接收主機發出的控制指令,并完成相應的功能。

(3)實現對DDS芯片的控制,根據需要選擇DDS不同的工作模式。

(4)實現對衰減器的控制,根據主機的命令選擇不同的頻率幅度。

5 結 語

通過對實際硬件電路的分析與調試,系統實現了計算機對USB芯片的控制、FPGA對DDS芯片的控制、偵察模塊與干擾模塊的互連通信以及各類干擾方式的可控實現。在進行實際試驗時,通過對不同干擾方式的效果進行比較,還可以選擇出對跳頻電臺通信最有效的干擾方式,并且對今后研究實戰形式的跳頻偵察干擾系統具有一定的實際參考意義。

參考文獻:

[1].AD6640datasheethttp://www.dzsc.com/datasheet/AD6640_1055397.html.

[2].ROMdatasheethttp://www.dzsc.com/datasheet/ROM_1188413.html.

[3].ACEX1Kdatasheethttp://www.dzsc.com/datasheet/ACEX1K_1307867.html.

[4].AD9854datasheethttp://www.dzsc.com/datasheet/AD9854_251860.html.

[5].AD5344datasheethttp://www.dzsc.com/datasheet/AD5344_1081777.html.

[6].FT245BMdatasheethttp://www.dzsc.com/datashee/FT245BM_335950.html.

評論