PCI總線接口技術及其在高速數據采集系統中的應用

*從模式操作

從模式就是允許PCI總線上的主控設備訪問局部總線上的PCI 9054的配置寄存器或內存,支持突發和單周期動模式傳輸。PCI 9054通過16字長的PCI從設備讀FIFO和32字長的PCI從設備寫FIFO來支持從PCI總線到局部總線上的突發或單周期的存儲器映射訪問和I/O映射訪問。PCI基址寄存器用來設定PCI存儲器和I/O空間的地址。從模式操作包括延時讀操作、提前讀操作等。

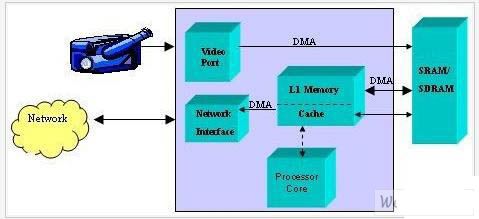

*DMA操作

PCI 9054有一個強大的雙通道分散/收集DMA控制器,支持PCI主機和適配器內存的高鏟公安廳發傳輸。兩個獨立的DMA通道能從局部總線到PCI總線和從PCI總線到局部總線傳輸數據。每個通道包括一個DMA控制器和一個專用雙向FIFO。兩個通道都支持塊傳輸、分散/收集傳輸、應用或者不用EOT傳輸等。模式選擇必須在PCI 9054成為一個PCI總線主設備之間主設備使能位(PCICR[2])使能。另外,兩個DMA通道都能編程實現8、16或32bit局部總線帶寬;使能/使無效內部等待周期;使能/使無效局部總線突發傳輸;執行PCI存儲器寫并無效操作;設置PCI中斷(INTA)或者是本地中斷(LINT)等。圖3和圖4分別描述了從PCI到局部總一和從局總總線到PCI總線的DMA數據傳輸操作邏輯。

4 采樣控制和驅動程序設計

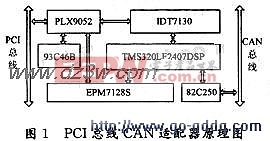

基于開發周期和成本考慮,本設計采用DMA傳輸模式。啟動采樣后,采和1KB×8的雙口SRAM IDT7130作為數據采集前端與PCI總線的數據緩沖,PCI 9054作為主控設備,利用其DMA通道進行數據傳輸。當雙口SRAM采滿1KB數據之后,通過EPLD(EPM7128)產生局部總線中斷,PCI9054獲得局部總線的控制權后,根據DMA的起始位將1KB的數據讀到DMA傳輸的專用FIFO中,PCI 9054申請占用PCI總線,獲得PCI總線的控制權后,將數據寫入PCI總線存儲空間,從而實現一次采樣和傳輸。

可編程邏輯器件(EPLD)用以實現PCI 9054與雙口SRAM的I/O邏輯、傳輸控制邏輯、中斷邏輯以及主機對數據采集通道的前端控制。

PCI數據采集卡另一關鍵問題是驅動程序的開發。設備驅動程序提供鏈接到PCI板卡的軟件接口,文件擴展名為.SYS的動態鏈接庫。在Windows98和Windows2000中,設備驅動程序必須根據Windows驅動程序模型(WDM)設計。設備驅動程序的關鍵是如何完成硬件操作,基本功能是完成設備的初始化、對端口的讀寫操作、中斷的設備和響應及中斷的調用,以及對內存的直接讀寫。本設計應用KRF-Tech公司的Windriver來編寫設備驅動程序,Windriver針對PLX和AMCC的專用接口芯片編寫了API函數包,降低了開發難度。

PCI 9054以其強大的功能和簡單的用戶接口,為PCI總線接口的開發提供了一種簡法的方法。設計者只需設計局部總線接口控制電路,即可實現與PCI總線的高速數據傳。在高速數據采集系統中,利用PCI總線的高速特性實時傳輸和存儲采集數據,有效地解決了數據傳輸和處理的實時性。隨著PCI總線的普及應用,基于PCI總線的采集系統設計有十分廣闊的前景。

評論