嵌入式UART接口模塊的設計

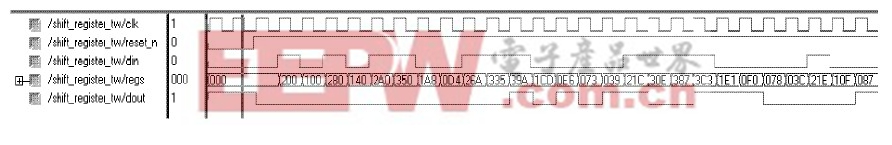

圖4 移位寄存器仿真波形圖

如圖4所示,移位寄存器在復位后的每個時鐘的上升沿工作。由于數據發送時是先發送有效數據的最低位,因此移位寄存器是將接收的數據由高位向低位移動,dout輸出移位寄存器的最低位。圖中的regs數據用16進制表示。

2.3 波特率發生器模塊

波特率發生器的功能是產生和RS232通信所采用的波特率同步的時鐘,這樣才能方便地按照RS232串行通信的時序要求進行數據接收或者發送。比如,波特率為9600b/s,即每秒傳輸9600b數據,則同步的波特率時鐘頻率為9600Hz,周期為1/9600=0.10417。

設計波特率時鐘的基本思路就是設計一個計數器,該計數器工作在速度很高的系統時鐘下,當計數器計數到某數值時將輸出置高,再計數到一定的數值后再將輸出置低,如此反復便能夠得到所需的波特率時鐘。該系統所用的FPGA系統時鐘為50MHz,RS232通信的波特率為9600b/s,則波特率時鐘的每個周期相當于

5208個系統時鐘周期。假如要得到占空比為50%的波特率時鐘,只要使得計數器在計數到1604時將輸出置高,之后在計數到5208時將輸出置低并且重新計數,就能實現和9600波特率同步的時鐘。

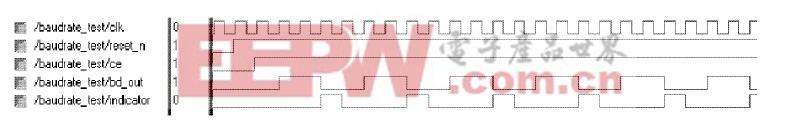

為了便于仿真,使計數器計到2時將輸出置高,之后計到4時將輸出置地并且重新計數。波特率發生器的仿真波形圖如圖5所示。

圖5 波特率發生器仿真波形圖

觀察波形可以看到波特率發生器每經過4個時鐘周期輸出1個完整的波特率時鐘周期,占空比為1/2,并且在每次輸出波特率時鐘周期之后輸出1個系統時鐘脈寬的提示信號indicator,UART通過此信號來了解波特率發生器已輸出的波特率時鐘周期個數。由波形圖可見波特率發生器的工作完全滿足設計的要求。

2.4 計數器模塊

計數器模塊的功能是可控的,在輸入時鐘的驅動下進行計數,當達到計數上閾時給UART內核一個提示信號。在不同的工作狀態下,計數器模塊的輸入時鐘是不同的。UART在數據發送之前需要進行數據加載(即將串行序列保存在移位寄存器內),在此工程中計數器模塊的輸入時鐘為系統時鐘,因為此時移位寄存器也工作在系統時鐘下。除了數據加載,另外2個需要計數器模塊的過程是數據接收和數據發送。

由于這兩個過程中移位寄存器工作在波特率時鐘下,所以計數器模塊的時鐘就是與波特率時鐘同步的波特率發生器提示信號indicator,這樣每輸出1個完整的波特率時鐘周期計數器就能增加1。

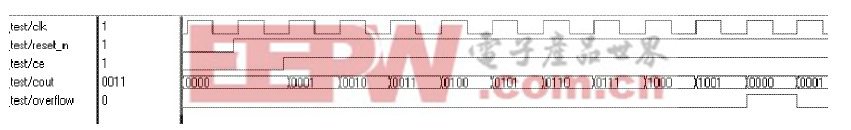

計數器的仿真波形圖如圖6所示。

圖6 計數器仿真波形圖

計數器在復位后并且ce有效時開始計數,并且在第10個時鐘周期輸出提示信號overflow。

2.5 發送數據緩沖器模塊

發送數據緩沖器模塊的功能是將要發送的并行數據轉換成串行數據,并且在輸出的串行數據流中加人起始位和停止位。緩沖器首先將要發送的8位數據寄存,并在最低位后添加起始位‘0’,在最高位前添加停止位‘1’,組成10位要發送的數據,然后根據UART內核模塊的計數值將相應的數據送入移位寄存器輸入端。

UART內核模塊輸出的計數值是從0依次計到9,即先將要發送數據的最低位送入移位寄存器。發送數據緩沖器的仿真波形圖如圖7所示。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論