一種基于FPGA的驅動接口電路的設計

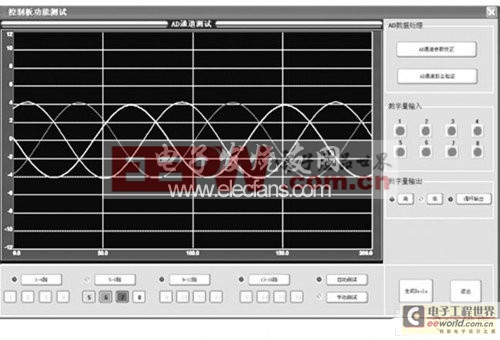

結合AD7862的轉換速度, FPGA選擇10MH z的處理時鐘。對于整個轉換過程的控制用一個狀態機來完成, 狀態機分為12 個狀態( idle, convert1, busy1, reada1, w ait1, reada2,sw apchna,l convert2, busy2, readb1, w ait2, readb2), 其中idle狀態為空閑等待轉換狀態; convert1指示第一次轉換啟動狀態;busy1指示第一次轉換狀態; reada1狀態下讀取VA1; wait1狀態為讀取VA1和VA2之間的等待狀態; reada2狀態下讀取VA2; sw apchnal狀態指示交換到另一個通道進行轉換;convert2指示第二次轉換啟動狀態; 剩余狀態和前面的類似,只不過是針對VB1 和VB2 而言。設計代碼如下( 只描述VA1和VA2的部分, 剩下的類似): process( clkdiv4, nrst) beg in if nrst = ‘0’ then adc_state = id le; e lsif( r ising _edge( clkd iv4) ) then case adc_state is when idle= > ada0 = '0' ; adconv = '1'; adncs = '1'; adnrd = '1'; clkcnt = 0; if( start= ‘1’) then adc_state = convert1; end if; w hen convert1= > ada0 = '0'; adconv = '0' ; if( adbusy= '1') then adc_state = busy1; end if; w hen busy1= > adconv = '1'; if( adbusy= '0') then adc_state = reada1; end if; when reada1= > if ( c lkcnt= 2) then addataa1 = 0000 adda tain; end if; if( c lkcnt= 4) then adc_state = w a it1; adncs = '1'; adnrd = '1'; clkcnt = 0; else clkcnt = c lkcnt+ 1; adncs = '0'; adnrd = '0'; end if; when wait1= > adc_state = reada2; when reada2= > if ( c lkcnt= 2) then addataa2 = 0001 adda tain; end if; 3設計電路的仿真驗證 最終設計用Quartus 2 軟件編譯綜合后在板上測試,FPGA 接口電路接受到的轉換數據傳給DSP芯片, 然后將DSP受到的數據用實時監控軟件顯示。圖3是給AD 輸入端加50 H z的正弦波信號(同時對其中三個輸入端加信號), 監控軟件顯示的波形。 從圖3波形圖可以看出, 接口驅動電路成功的控制了AD7862芯片的采樣過程, 從而驗證了驅動電路設計的正確性。

圖3 軟件顯示波形圖。

評論