基于Altera ASI IP核的ASI發送卡實現

在ASI 的編碼過程中,只需將MPEG-2 編碼的TS 碼流的8 位數據和一位TS 碼率傳輸時 鐘輸入到FPGA 中,本方案是PCI 33M 的時鐘信號。因為在本方案中,TS 格式為188 個字節 的突發模式發送數據,根據數據有效信號DVALID,FPGA 檢測這個信號來判斷什么時間內是 有效數據,來接收TS 碼流數據,而不用關心TS 碼流的同步頭。FPGA 將接收到的數據以TS 碼率時鐘寫入FIFO。當FIFO 半滿時,FPGA 接收到FIFO 的半滿信號,然后FPGA 給ASI 核發出FIFO 可讀信號,ASI 核以27Mbps 讀取FIFO 中的數據;當FPGA 計數到ASI 核讀取了一定數量的FIFO 數據,FPGA 則向ASI IP 核發送FIFO 不可讀信號,防止FIFO 讀空。MPEG-2 傳 輸碼率的并行最大速度為132Mbps,而讀FIFO 速率為27Mbps,因此FIFO 會有溢出。因此在發送MPEG-2 傳輸流時,有驅動程序控制一次發送數據的多少。考慮到延時,本方案在FPGA 內部燒制了一個2K 大小的異步FIFO。ASI IP 核在FIFO 中數據不可讀時,向ASI 碼流中填 充K28.5 以維持270Mbps 的固定傳輸速率。最后串行數據經過驅動就可用同軸電纜傳送出去。 本方案中,同步字K28.5 的插入采用傳輸碼流的單個字節前后不能都是K28.5 同步字的方式。

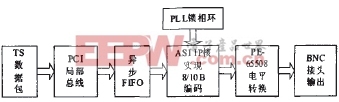

ASI 發送卡的硬件實現框圖如下:

該系統是基于 ALTERA 公司的FPGA 芯片,Cyclone Ⅱ EP2C8Q208 設計的。經過編碼的并行數據流經過PCI 總線送入異步FIFO。異步FIFO 主要實現數據緩存和時鐘匹配的作用。 系統進行DMA 操作,把數據送入板卡。FIFO 將這些數據緩存,以避免數據丟失。又由于時 鐘有PCI 33M 的時鐘信號和27M 的ASI 輸入時鐘信號。這就要求把這兩個不同頻率的時鐘同 步。FIFO 在兩個不同的時鐘下工作,數據的輸入和輸出分別使用不同的時鐘。這就實現了 時鐘的隔離和無縫連接。FIFO 采用32 位輸入、8 位輸出,分別與PCI 的數據寬度和ASI IP 核的輸入數據寬度相一致。ASI IP 核實現8 位數據到10 位的編碼。其中ASI IP 核的參考 時鐘為27M,輸出時鐘是270M。采用外部鎖相環,27MHz 時鐘頻率有晶振產生,通過鎖相環 產生270M 的時鐘,用于ASI 接口的數據輸出。PE65508 實現耦合和阻抗匹配,最終經BNC 插頭發送出去。

3.2 ASI IP 核的生成

ASI 編碼的實現采用Quartus 6.1 直接生成,進行仿真驗證。

ASI 接口的生成。IP 核首先需要安裝,可以從Altera 網站上下載。安裝之后,打開 Quartus 6.1 新建工程之后,點擊tools 菜單里面的Megawizard plug-in Maneger,選擇 創建一個新的宏函數變量,按步驟一步步生成asi 文件。可以選擇器件和生成文件語言,分 別選擇Cyclone Ⅱ和verilog 語言。需要注意的是生成的文件名要與工程的頂層文件名相 一致。選擇Transmitter,這里作為發送接口。在ASI 中根據所選器件速度的快慢,可以選 擇是否生成鎖相環。這里采用外部鎖相環,用于產生270MHz 的輸出頻率。

生成的ASI 接口verilog 部分代碼如下:

module asi ( rst, tx_refclk, tx_data, tx_en, tx_clk270, asi_tx);

input rst,tx_refclk,tx_en,tx_clk270,asi_tx;

input [7:0] tx_data;

asi_megacore_top asi_megacore_top_inst( .rst(rst), .tx_refclk(tx_refclk), .tx_data(tx_data),

.tx_en(tx_en), .tx_clk270(tx_clk270), .asi_tx(asi_tx));

……

endmodule

該接口實現8 位數據到10 位數據的編碼。在8 位的MPEG-2 數據從輸入端輸入,流入內 部FIFO 中。tx_data 8 位并行數據輸入接口,實現數據編碼,即把每個8 位的數據變為10 位的數據;然后串行器把10 位并行數據轉換為串行數據。asi_tx 經編碼后的串行數據輸入 接口。若MPEG-2 的TS 流的傳輸率小于270Mbps 時,則需要插入同步字符以保障輸出端穩定 的270Mbps。tx_refclk 為輸入的27M 參考時鐘,tx_clk270 為270M 的數據輸出時鐘。它們是通過外部鎖相環得到的。rst 是復位信號,高電平是有效電平,使整個設計停止工作。tx_en 數據輸入使能信號,控制FIFO 中待編碼的數據進入ASI IP 核實現數據編碼和并串轉換。

3.3 ASI 工程及仿真波形

把生成的ASI 核添加的自己的工程中,頂層部分代碼如下:

module FIFO_ASI(clk27,data,t_out);

input clk27;

output data,t_out

wire clk13,clk270;

wire[31:0] data32;

wire[7:0] data8;

……

endmodule

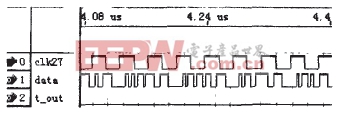

對其進行仿真,波形如下:

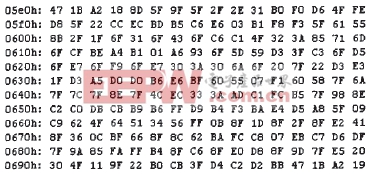

外部接 27M 的時鐘,連接到clk27,做為ASI IP 核27M 的輸入參考時鐘。t_out 為一個 時鐘輸出信號,對27M 分頻,作為指示燈信號,來監測程序是否下載到FPAG 中。在指示燈正常閃爍情況下,表明程序已經下到芯片中,并且能夠工作。經過ASI IP 核編碼的ASI 數 據由data 輸入。在本工程中,通過一電腦不斷地發送TS 流給板卡,經過ASI 編碼后通過 ASI 接口輸出。在接收端,通過一個ASI 接收卡,讀出接收的數據,可以看出ASI 工作正常。 在發送TS 流時采突發模式,其讀出的數據如下:

在調試階段,PC 機連續發送相同的MPEG-2 編碼的TS 包。在接收到的數據中,可以看到連 續的MPEG-2 編碼的TS 包,且與發送的數據相同。其中TS 包的接收采用一塊ASI 接收卡作 為接收端,通過USB 接口輸入到電腦里,用相應的軟件讀取數據后顯示。

4.應用意義

本文設計的基于Altera 公司的ASI IP 核實現的DVB-ASI 卡,實現了ASI 數據的正確編 碼和發送。用FPGA 實現邏輯控制和數據緩存,可以方便的實現系統升級,實現多個ASI 數 據的發送。與用Cypress 公司的CY7B923 實現的ASI 的發送卡相比,本卡更適合批量生產,可以節約成本,提高了市場竟爭力,具有很好的市場前景。

本文作者創新觀點是用Altera 公司的ASI IP 核代替Cypress 公司的CY7B923 專用ASI 發送芯片,實現ASI 數據的穩定發送。本方案降低了成本,設計靈活,并且方便升級到多路ASI 數據發送。

評論