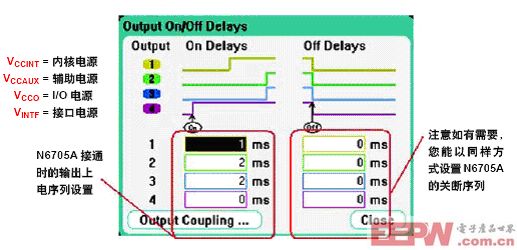

首先按照 圖2 所示,為FPGA電路設置上電時序,VINTF 最早打開輸出,VCCINT 在VCCO 之前1毫秒打開供電:

圖2 N6705A上電序列設置屏

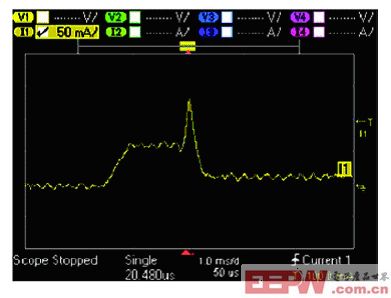

在此供電情況下,可以看到內核電源消耗的電流 ICCINT 在上電過程中產生一個明顯的脈沖尖峰,如圖3 所示:

圖3 內核電源VCCINT在上電過程中所消耗的電流波形ICCINT

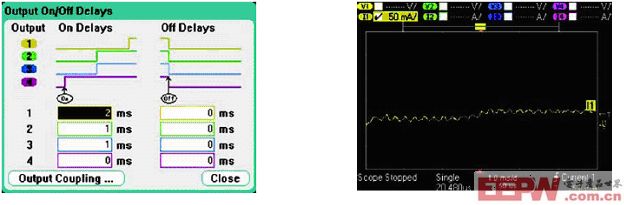

按圖4 所示重新改變上電時序,使VCCINT上電輸出滯后于VCCAUX 1毫秒,此時可以看到ICCINT 電流波形中脈沖尖峰已經消失。

圖4 調整上電時序后,ICCINT 的電流波形

評論