基于DSP、DDS和ARM雷達中頻信號模擬器研究

2.3.2 時鐘設計

DDS輸出的信號的頻譜特性在很大程度上取決于參考時鐘的頻譜特性,參考時鐘的一些主要特性如相位噪聲、時鐘抖動以及頻率穩定度都直接地反映在DDS的輸出信號上。DDS的時鐘電路能否設計達到高穩定、低噪聲、精確同步直接影響本系統性能的優劣。AD9852的參考時鐘可以采用單端輸入或差分輸入,由于差分信號可能有效抑制共模噪聲和電磁能量外泄,根據AD9852對峰峰值的要求(>400mV),本設計采用差分LVPECL邏輯。

本模塊采用40MHz的晶振,經緩沖器CY2305輸出三路同步時鐘,如圖3所示。其中一路接SH853501,將一路LVCMOS時鐘變成三路差分LVPECL時鐘后,分別傳送給三片AD9852,經片上鎖相環倍頻形成DDS的系統時鐘;一路給時序控制模塊EPLD,將時鐘信號分頻后產生三片AD9852的I/O更新時鐘;另一路作為同步時鐘供給信號處理機。

2.4 通信模塊

雷達模擬器與CP機間采用USB通信協議,由S3C44B0X控制USB接口器件ISP1581實現。DSP可以通過控制EPLD給信號處理機發送目標角度信息,也可以利用多通道緩沖串口向處理機傳送目標信息。本系統提供了衰減控制接口,由DSP產生相應的衰減控制字,傳給鎖存器SN75LVC574,控制處理機上的數控衰減器。

3 相參脈沖雷達動目標信號的模擬

本系統中的三片DDS以及控制刷新和工作時序的EPLD采用同一個時鐘源,并向信號處理機提供同步時鐘輸出,因此應用本系統可設計中頻相參雷達信號的模擬。

本設計中,信號處理機利用信號模擬器輸出的同步時鐘,將其分頻生成觸發脈沖,送給模擬器DSP的外中斷源4,觸發脈沖的周期對應雷達信號的PRT(脈沖重復周期)。EPLD分頻時鐘的周期對應雷達脈沖信號的脈寬,該信號提供AD9852的I/O更新時鐘,同時接DSP的外中斷源5。使用兩路DDS。DDS1模擬動目標回波,DDS2模擬雜波信號。

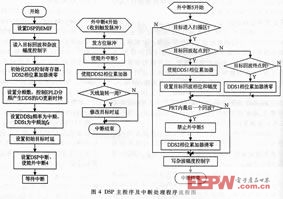

在PC機上,根據要模擬的目標及環境特性,通過建立相應模型,計算生成目標回波及雜波的幅度控制字存儲。DSP主程序首先將這些數據讀入SDRAM。在設計定的目標角度范圍內,每次接收到觸發信號,經由目標距離決定的延時,DSP中斷產生一個目標回波信號。信號的頻率和相位包含目標運動的多普勒頻率信息,幅值從SDRAM讀入;雜波采用DDS2連續輸出產生,每隔一個脈沖持續時間DSP進入一次中斷,讀取SDRAM改變雜波的幅值。DSP主程序及中斷處理程序流程如圖4所示。

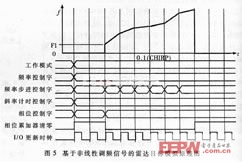

以上模擬過程采用的雷達信號為簡單矩形脈沖,脈寬等于DDS更新信號的周期。如果采用大脈寬,在脈寬內每個DDS更新時鐘到來時,按照巴克碼或M序列改變信號的相位,可模擬相位編碼脈沖壓縮信號。當AD9852工作在CHIRP模式下,通過設置頻率步進步長和斜率計時(即變化的頻率在每個頻率點上停留的時間)控制字,可模擬線形調頻脈沖壓縮信號。在同一模式下,若在脈寬內每個DDS更新時鐘到來時改變頻率步進步長或斜率計時控制字,可模擬非線性一調頻脈沖壓縮信號,其原理如圖5所示。

本設計主要具有以下特點:

(1)利用AD9852的多種工作模式,可方便產生多種雷達信號,而且頻率捷變速度快,捷變時相位連續,頻率分辨率高達10-6Hz。

(2)通過TMS320C6416同時控制三片DDS,讀寫速度快,保證了實時性和輸出信號相位相參數。

(3)通過ARM控制USB模塊和DSP主機口,可實時修改信號參數和加載新的程序及數據。

(4)采用三路DDS,并提供同步時鐘輸出,為適應不同體制雷達的要求提供了保證,更具通用性。

實驗和應用結果表明,該系統能夠模擬多種體制的雷達中頻信號,而且不同信號間切換方便,使用靈活。該系統為雷達中頻信號模擬提供了一個通用的硬件平臺。在此基礎上,通過豐富和完善軟件數據庫,可建成通用雷達中頻信號模擬系統。

評論