PCB設計:如何減少錯誤并提高效率

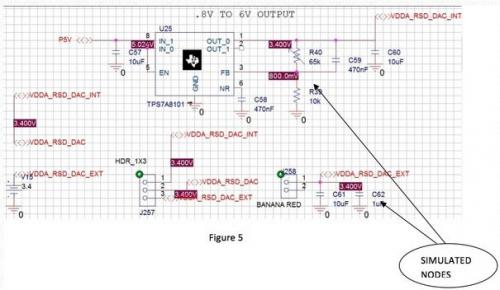

為了驗證連接關系并執行整體檢查,使用了原理圖仿真。原理圖仿真由原理圖創建、測試平臺創建和仿真組成。

本文引用地址:http://cqxgywz.com/article/269192.htm在測試平臺創建過程中,將有激勵信號給到必要的輸入端,然后在感興趣的信號點觀察輸出結果。

可以通過將探針連接到待觀察節點實現上述過程。節點電壓和波形可以指示原理圖有沒有錯誤。所有信號連接都會得到自動檢查。

圖4:原理圖測試平臺和各個節點的仿真值。

讓我們看一下上面這張圖的一個局部,其中探測的節點和電壓清晰可見:

因此在仿真的幫助下,我們可以直接觀察結果,確認電路板原理圖是否正確。另外,通過仔細調節激勵信號或元件值還可以實現設計更改的調查。因此原理圖仿真可以節省電路板設計和檢查人員的大量時間,并且增加設計正確性的機會。

評論