一種ARM+DSP協作架構的FPGA驗證實現

3.4 軟硬件協同驗證

本文引用地址:http://cqxgywz.com/article/83026.htm軟硬件協同驗證是較好的驗證方式(或調試方式),二者都是為了保證系統功能和結構正確的有效手段。在整個FPGA系統實現過程中,非常有必要結合前端軟件仿真波形來參照調試系統各個環節的功能運行情況,這樣可以大大簡化研發進程,有效地縮短調試周期。可以說,如果不結合前端軟件仿真波形來協同驗證的話,要想實現一個較為復雜的體系結構是非常困難的。

一般而言,對于這樣一個較為復雜的體系結構需要先進行前端RTL代碼的軟件仿真,因為前端仿真對于糾正RTL級代碼以及功能方面的錯誤是非常方便的,而且它所需要的驗證周期和糾錯難度比硬件的FPGA驗證要有利得多。但是FPGA硬件驗證,其真實性又是非常可靠的。所以驗證波形完全調試通過之后,可以非常有效地指導FPGA的實現。當FPGA在調試某項功能時出現了問題,可以通過邏輯分析儀將可疑端口節點出來的觀測點波形導出來對照軟件仿真波形來查找問題,這是一種非常有效的手段。

3.5 Demo演示速度的調整

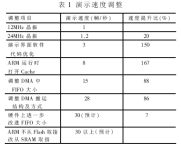

目前,開發板選用的晶振頻率為24MHz,穩定的演示版本速度能夠達到28幀/秒,為人眼所能接受的連續視頻速度,效果已經相當好。這是經過了各種調試才達到的效果。主要原因在于考慮比較周全:DMA在傳輸圖像序列的時候,所用到的FIFO在設計之初就考慮到了FPGA的容量和利用率,認識到其容量有限,在現有的FIFO容量下,要想調整到一個DMA與PC機雙方網口傳輸速度的精確狀態不太容易,如果運行速度太快,交互同步不準確,就會有丟包的現象發生;如果為了更方便的調試和達到更好的速度性能,可以選用更大容量的FPGA,設計更大容量的FIFO,這樣每一次圖像傳輸就可以傳送更多的圖像數據,減少DMA搬運的次數,傳輸雙方的交互過程較為容易控制。表1給出了從開始演示速度不理想到較為理想所做的調整過程。從表1中可以看出,單獨調整晶振頻率,速度提升并不明顯。這說明了速度瓶頸不在硬件代碼性能上,關鍵在于演示界面的軟件代碼、ARM的Cache打開與否以及圖像搬運的速度三方面。同時還可以看出Cache的打開對于速度影響很大,說明ARM的取指速度受到影響。目前ARM的運行指令是放在Flash中,如果改成從SRAM中取指,估計效果會更加理想。

從以上分析可見,ARM在整個設計中所起的主要作用是控制圖像的輸入輸出,以及循環控制DSP Core的運行停止等狀態;DSP Core的主要作用是處理運算應用程序,計算小目標識別程序。這樣既分工又合作,能夠充分發揮ARM的控制功能以及DSP Core的數字運算處理功能。

與此同時,由于ARM在整個設計當中主要起到一些輔助的控制作用,ARM922T的一些擴展DSP運算功能沒有用到,如果綜合考慮到成本和性價比等因素,可以考慮采用ARM7硬核、NIOS 或其他形式的軟核替代。

參考文獻

[1] FURBER S,田澤,于敦山.ARM SOC體系結構.盛世敏,譯.北京:北京航空航天大學出版社,2002.

[2] CSCHWIND M. FPGA prototyping of a RISC processor core for embedded applications. IEEE Transactions on Very Large Scale Integration(VLSI)Systems,2001,9(2).

[3] Hardware Reference Manual Version 3.1. www.altera.com 2002-11.

評論