采用West Bridge架構提升系統性能、縮短開發周期、并降低便攜式消費類電子產品的成本(08-100)

West Bridge Astoria具有三個接口:一個處理器“P”端口、一個高速USB“U”端口,以及一個海量存儲“S”端口。“P”端口支持嵌入式處理器連接,同時還支持硬件 DMA 存取。Astoria采用靈活而可配置的“P”端口,可支持不同處理器上的各種標準接口。“U”端口提供USB2.0高速USB鏈接,“S”端口經配置后能夠支持各種海量存儲器件,如 SD/SDHC、SDIO、MMC、CE-ATA以及SLC/MLC NAND 等。

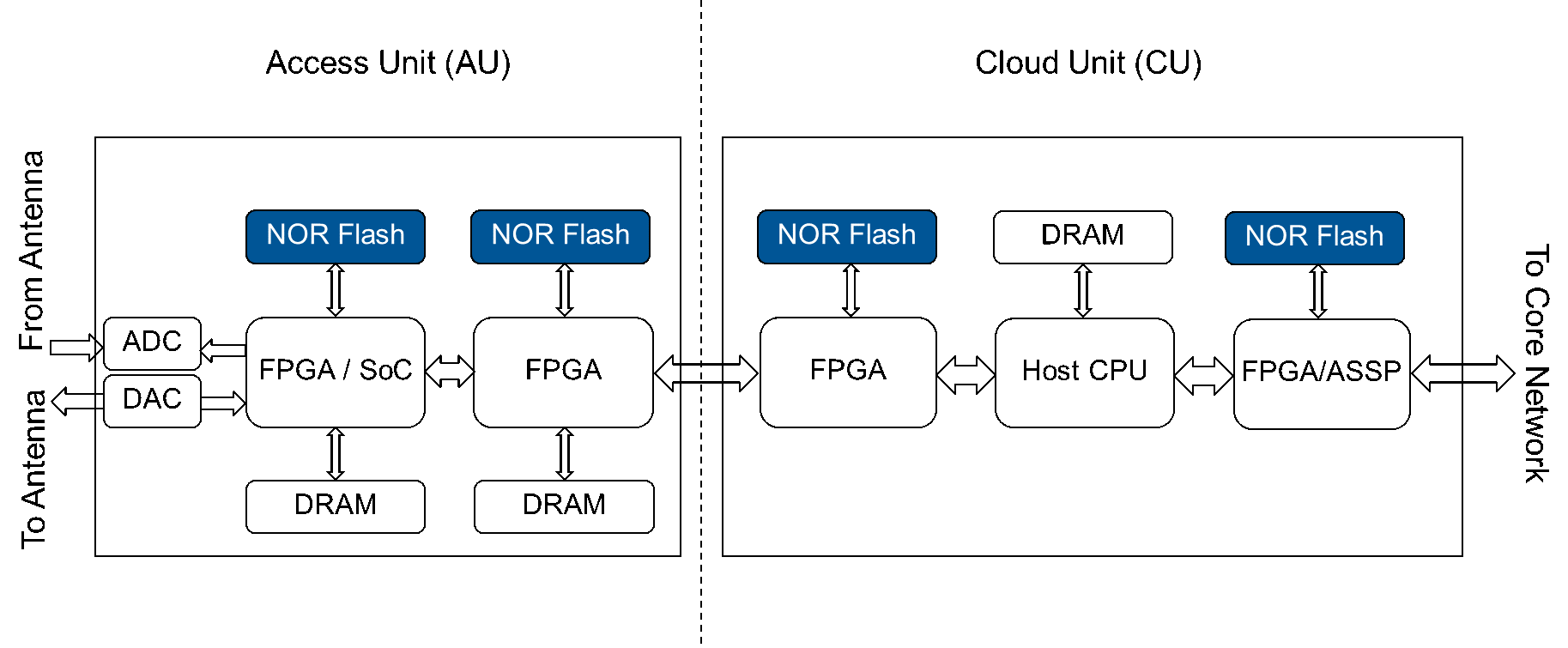

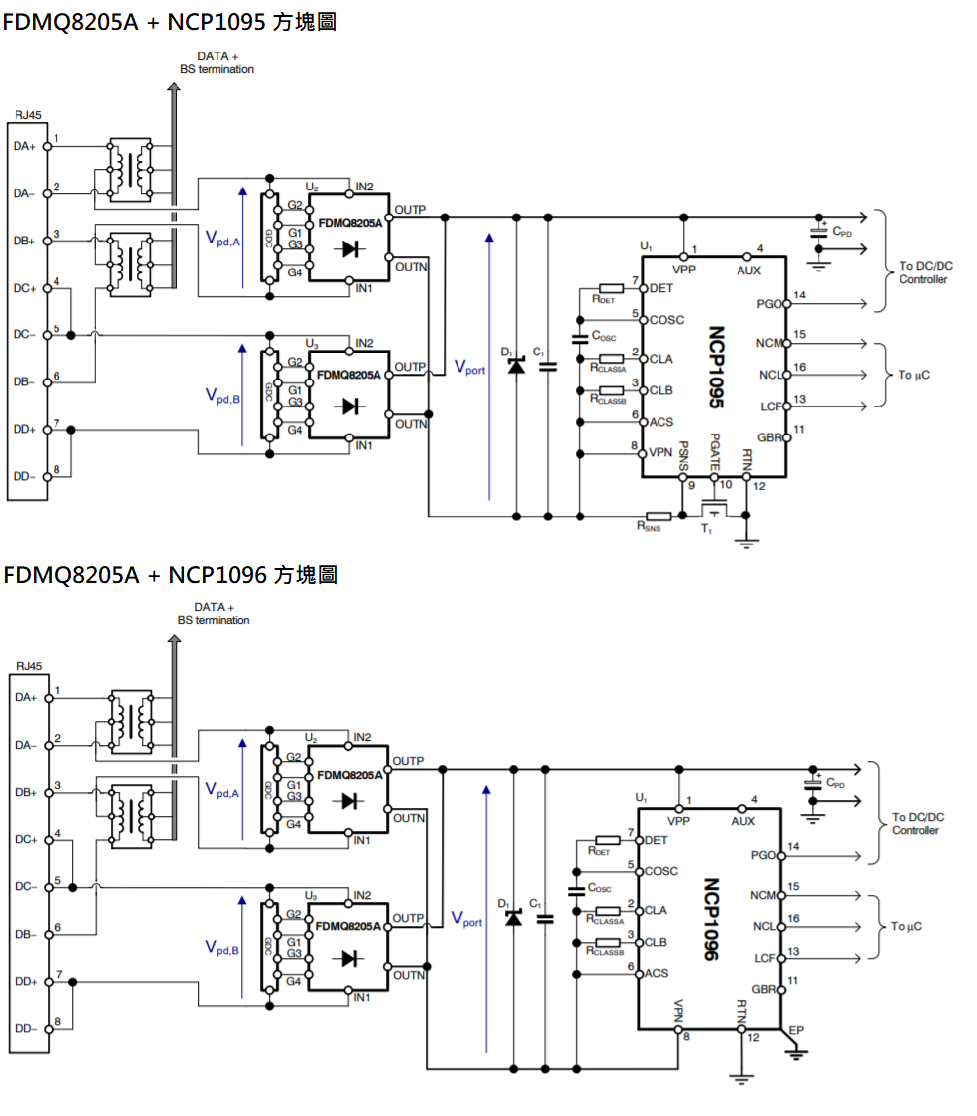

本文引用地址:http://cqxgywz.com/article/91683.htm圖1中的紅色箭頭顯示了三個端口之間可能的數據路徑,其中所采用的是 West Bridge Astoria實現了革命性突破的至獨立多媒體的同時鏈接 (SLIM) 架構。該 SLIM構架使所有三個數據路徑能夠同時運行,從而實現海量存儲與外設功能的多任務執行。

支持最新標準

如前所述,當前市場上的嵌入式處理器不能為最新的海量存儲和外設標準提供足夠的支持,有時甚至完全不能支持。West Bridge 能支持 USB 2.0 高速等最新的外設連接標準,此外還支持 SLC/MLC NAND、SD2.0 SDHC/SDIO、MMC4.2 以及 CE-ATA 等新型海量存儲器件。West Bridge器件的設計周期也大大比完全成熟的處理器設計周期要短。因此,我們可以預見,就像 PC 領域的南橋、北橋一樣,West Bridge 將成為嵌入式系統的必需的處理器,來支持最新的技術標準。

優化的高速USB與海量存儲性能

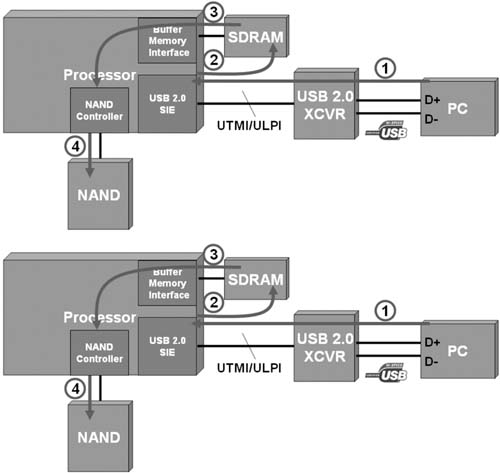

圖 2 顯示了 USB 2.0 高速實施方案的典型示例,其中的嵌入式處理器集成了高速 USB SIE 與外部收發器。從PC傳出的數據首先穿過高速USB2.0信號高速管道,并緩沖至 SDRAM 中。處理器隨后從SDRAM讀取數據,并寫入海量存儲設備。這一系列中間傳輸機制不僅會防礙系統充分發揮高速USB的性能,而且還會在軟件未經認真優化的情況下顯著拖慢整體系統速度。因此,采用這種架構通常不能獲得最佳的消費者使用體驗。

圖 2 帶集成高速 USB 控制器的系統數據流程

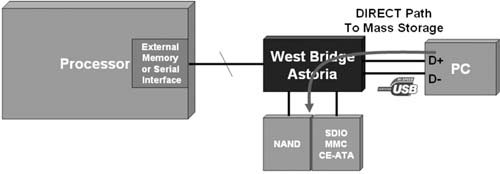

與圖2所示的架構不同,圖3顯示的West Bridge架構能夠直接將存儲器件連接至West Bridge。數據傳輸完全不會占用處理器資源,因為處理器不再位于數據路徑上,從而讓處理器留下更多的帶寬,使處理器能夠擁有更多的資源來處理更重要的任務。

圖3 采用West Bridge實現的從PC到海量存儲單元的直接數據路徑

評論