多路同步串口的FPGA傳輸實現

信號抗干擾處理

本文引用地址:http://cqxgywz.com/article/94602.htm在FPGA和ARM之間的通訊中利用差分信號傳輸用于消除信號的干擾。差分對是指兩條線路總是傳送相反的邏輯電平,差分對信號對外界干擾源產生的噪聲不敏感,例如電路板的干擾噪聲等。

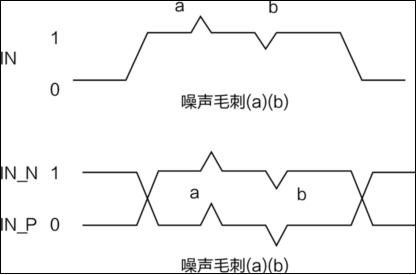

如圖7所示[5],IN引腳連接一個信號源,可以看到,對a噪聲毛刺不敏感,但是對于b噪聲毛刺,卻有可能使其誤認為一個脈沖,而這個可能引起FPGA內部的一些不期望的行為,如讀出一個錯誤的值。

圖7 差分降噪處理原理

差分對中的兩個信號總是傳送互補的邏輯值,所以當上圖中的IN_P為邏輯1時,IN_N則為邏輯0,反之亦然。并且布線時,差分對的兩條線路布線得非常的近,因此噪聲對他們的影響都是相同的。接收端只對兩個信號的差異感興趣,若兩個信號相同,則對此不敏感。

評論