- 摘 要:介紹了用Multisim 仿真軟件測試門電路延遲時間的方法,提出了三種測試方案,即將奇數個門首尾相接構成環形振蕩電路,用虛擬示波器測試所產生振蕩信號的周期,計算門的傳輸延遲時間;奇數個門首尾相接構成環形

- 關鍵字:

Multisim 門電路 仿真測試 方案

- 引 言

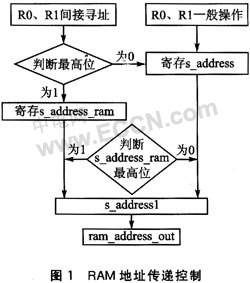

80C51系列單片機是一類經典的8位微處理器,其設計方法和體系結構一直是其他各類單片機設計的參考典范,自從20世紀80年代面世以后,得到了極大的發展與應用。直到今天,市場上還有一大部分單片機應用成品將其作為處理核心。基于80C51系列單片機無知識產權保護、市場應用廣泛等優點,對其進行功能拓展,既有利于經濟上節約成本,也有利于成果的推廣使用。而隨著單片機應用日趨復雜化,傳統的51系列單片機在設計上的不足逐漸顯現出來。如在現有128字節內部RAM基礎上,處理一些比較復雜的算法就顯不足。鑒于此

- 關鍵字:

RAM 單片機 微處理器 IP核 仿真測試

仿真測試介紹

您好,目前還沒有人創建詞條仿真測試!

歡迎您創建該詞條,闡述對仿真測試的理解,并與今后在此搜索仿真測試的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473