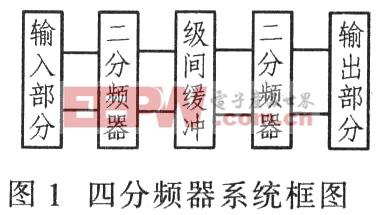

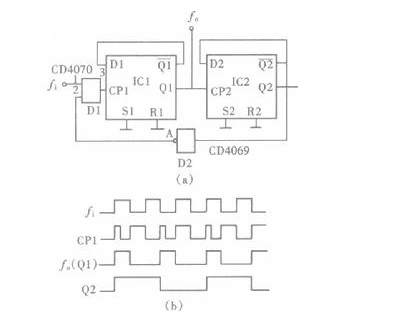

引言 分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求奇數倍分頻(如3、5等)、小數倍(如2.5、3.5等)分頻、占空比50%的應用場合卻往往不能滿足要求。

關鍵字:

CPLD FPGA 多功能 分頻器

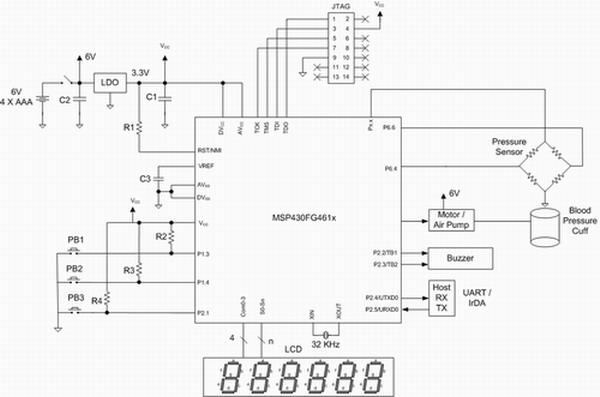

目前,醫療電器 OEM廠商正在開發技術含量更高的、用于治療和監控常見疾病的個人保健設備。這些產品價格合理,極大提高了醫療保健質量。MCU在家用血壓計、肺活量計、脈搏血氧計及心率監測器等便攜式醫療設備中起著重要作用。大多數此類產品中的實際生理信號是模擬信號,在測量、監控或顯示前需要進行放大、過濾等處理。

將高性能模擬外設嵌入超低功耗 MCU 中,不僅可以實現便攜式醫療電子設備的片上系統化,而且還可延長電池使用壽命。本文將介紹簡化便攜式電池供電醫療設備的模擬前端設計的多種方法,如將運算放大器、ADC

關鍵字:

分頻器 信號調理 數據采集器

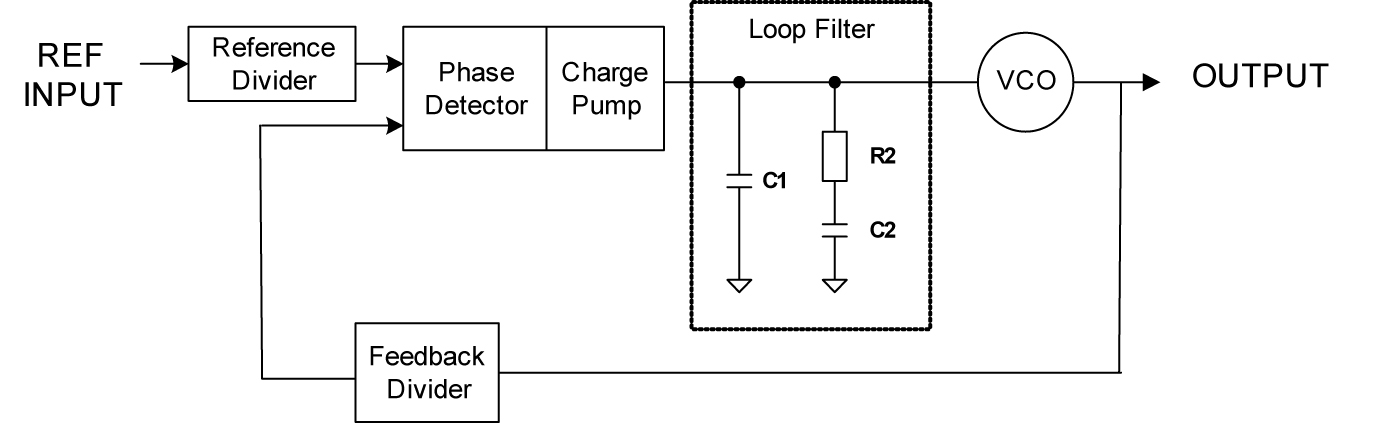

多年以來,作為業界主流產品的模擬PLL已被熟知,模擬PLL性能穩定,可為頻率合成和抖動消除提供低成本的解決方案,工作頻率高達8GHz及以上。然而新興的基于直接數字頻率合成(DDS)的數字PLL在某些應用中極具競爭力。本文比較了模擬PLL和基于DDS的數字PLL之間的差異,以及如何利用這些差異來指導設計人員選擇最佳的解決方案。

數字PLL利用數字邏輯實現傳統的PLL模塊。雖然實現數字PLL的方法有很多,但本文只介紹基于DDS的數字PLL架構。

圖1 典型的模擬PLL結構框圖

關鍵字:

PLL DDS 分頻器 鑒相器 DAC VCO

概述

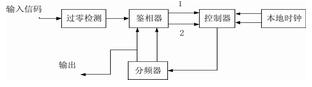

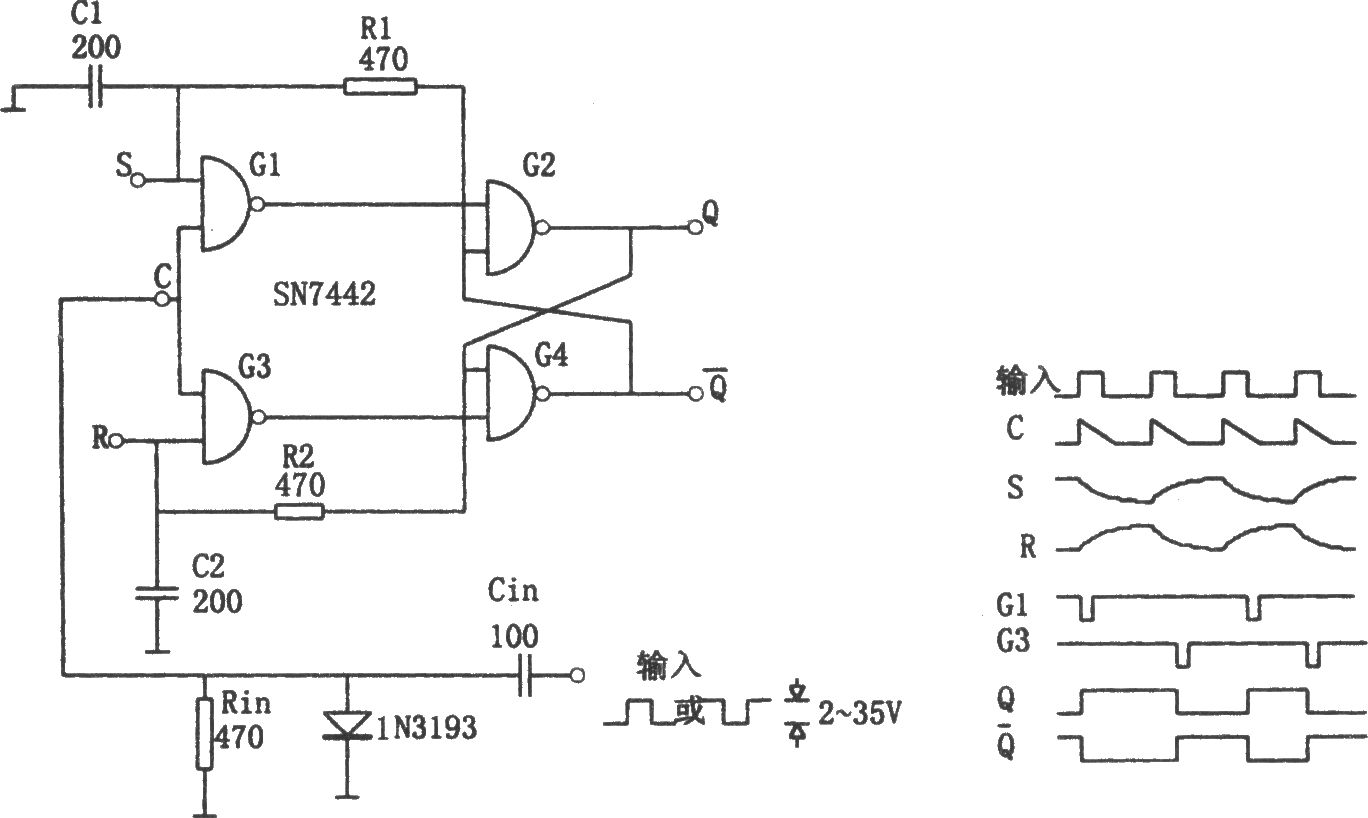

同步是通信系統中一個重要的問題。在數字通信中,除了獲取相干載波的載波同步外,位同步的提取是更為重要的一個環節。因為只有確定了每一個碼元的起始時刻,才能對數字信息作出正確的判決。利用全數字鎖相環可直接從接收到的單極性不歸零碼中提取位同步信號。

一般的位同步電路大多采用標準邏輯器件按傳統數字系統設計方法構成,具有功耗大,可靠性低的缺點。用FPGA設計電路具有很高的靈活性和可靠性,可以提高集成度和設計速度,增強系統的整體性能。本文給出了一種基于fpga的數字鎖相環位同步提取電路。

數

關鍵字:

FPGA 鎖相環 分頻器

摘 要:本文提出了一種5.8GHz微波頻率源的設計方法,較為詳盡地分析了該系統各組成部分的性能及參數,并對系統參數做了總結。關鍵詞:相位噪聲;分頻器;LPF

本文設計的5.8GHz微波頻率源主要應用于專用短程通信系統(Dedicated Short Range Communication,簡稱DSRC),未來DSRC的標準也傾向于使用基于5.8GHz的微波通信。如圖1所示,專用短程通信系統采用的是無線通信技術。根據實際DSRC系統設計的方案,本文所設計的5.8GHz微

關鍵字:

LPF 分頻器 相位噪聲

簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數分頻器的設計為例,介紹了在MAX+plus II開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過程和方法。

關鍵字:

CPLD FPGA 整數 分頻器

分頻器介紹

分頻器定義

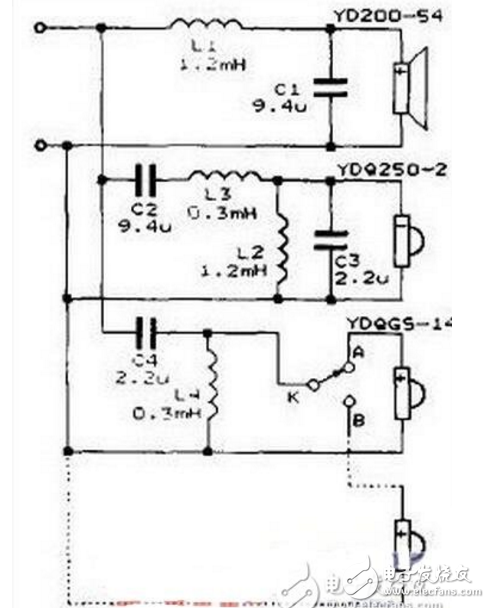

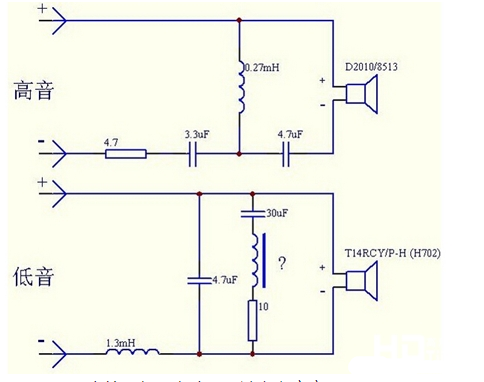

分頻器是音箱內的一種電路裝置,用以將輸入的音樂信號分離成高音、中音、低音等不同部分,然后分別送入相應的高、中、低音喇叭單元中重放。

分頻器是指將不同頻段的聲音信號區分開來,分別給于放大,然后送到相應頻段的揚聲器中再進行重放。在高質量聲音重放時,需要進行電子分頻處理。

分頻器作用

分頻器是音箱中的“大腦”,對音質的好壞至關重要。功放輸出的音樂訊號必須經過分頻器 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473