- 當今的設計工程師受到面積、功率和成本的約束,不能采用GHz級的計算機實現嵌入式設計。在嵌入式系統中,通常是由相對數量較少的算法決定最大的運算需求。使用設計自動化工具可以將這些算法快速轉換到硬件協處理器中。

- 關鍵字:

FPGA 協處理器 算法

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

pcm模塊 basic語言 協處理器

- IPS體系結構中的系統控制協處理器簡稱CP0,它提供指令正常執行所需的環境,進行異常/中斷處理、高速緩存填...

- 關鍵字:

嵌入式CPU 系統控制 協處理器

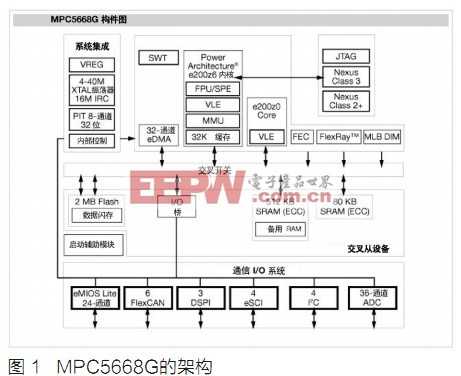

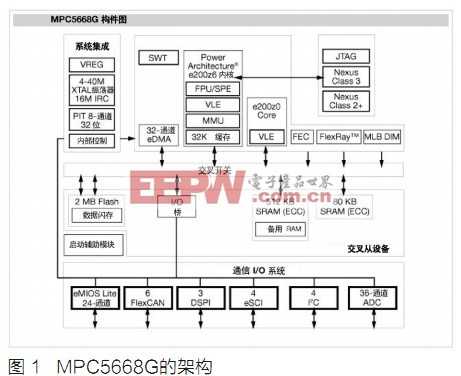

- 集成了數據通信、本地服務和視頻娛樂功能的高端汽車信息娛樂系統需要高性能的可編程處理技術支持,將FPGA協處理器整合進主流汽車信息通訊系統架構是最理想的解決方案。本文提出了汽車娛樂系統的要求,討論了主流系統

- 關鍵字:

FPGA 協處理器 汽車信息娛樂 通訊系統

- 上周Intel正式公布了新一代“集成眾核”架構MIC協處理器Knight Corner,和之前上代Larrabee繼承者Knights Ferry不同的是,新的Knights Corner從外表上看是采用與Xeon類似的LGA/BGA封裝。從這點來看,集成50個x86核心,運算能力達到1TFLOPS的Knights Corner可能會放棄“加速卡”的形式,采用QPI總線替代PCI-E界面。

- 關鍵字:

Intel 協處理器

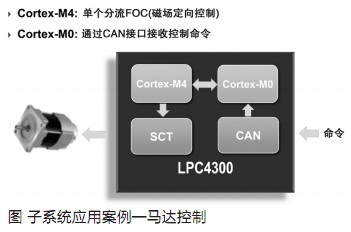

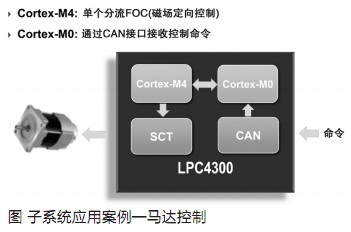

- 不管單核的運行頻率有多高,在執行多個任務時,它始終存在性能瓶頸和一些挑戰。以較高頻率運行的單核會消耗更多的功率。因此,單核架構無法滿足超低功率應用的需求。與基于單核的架構相比,基于雙核的SOC架構在性能和功率消耗方面實現了更好的平衡。

因此,雙核SoC目前已經被大量應用于汽車設計。除了提供比單核更高的性能外,基于雙核的架構還被用于安全應用。安全性是汽車制造商比較關心的主要問題之一。隨著更多復雜應用的引入,硬件或軟件出現故障的機率也大大增加。汽車的設計必須足夠可靠,從而能夠檢測出任何故障并采取相應

- 關鍵字:

Freescale 協處理器 異構雙核架構

- MCU通常通過主處理器和協處理器架構形成多核;在高性能處理器(MPU)中,同構核、異構核紛繁復雜,對軟件編程形成了挑戰,需要仿真、虛擬化等技術來實現。

- 關鍵字:

多核 協處理器 虛擬化 仿真器 M2M 201012

- 日前,德州儀器 (TI) 宣布推出可針對各種移動市場實現高達 2,000 萬像素 (20 MP) 拍照功能以及 720p 高清 (HD) 攝像功能的 OMAP-DM515 與 OMAP-DM525 協處理器,進一步壯大了 OMAP-DM5x 協處理器產品陣營,從而可進一步滿足消費者對具備可堪比單機產品性能的手機的需求。OMAP-DM515 與 OMAP-DM525 協處理器大幅提高了成像與視頻性能,使手機制造商輕松實現當前手機設計的升級,縮短上市時間,提供最先進的多媒體功能。

OMAP-DM

- 關鍵字:

TI 協處理器 OMAP-DM5x

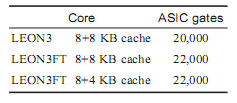

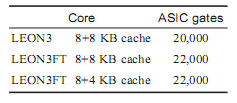

- 介紹了LEON3處理器和Speed協處理器的基本情況,提出了替代FPGA控制方式的LEON3可編程方案,方便了用戶使用Speed;開發了AHB總線接口、DMA控制器,并詳細敘述了軟硬件聯合開發的互動過程;軟硬件仿真結果證明了此方案的正確性、可行性和實用性。

- 關鍵字:

SoC DMA LEON3 協處理器 AHB 200905

- 基于C的設計方式簡化FPGA/協處理器混合平臺軟硬件協同設計

在最近幾年中日益流行在高性能嵌入式應用中使用現場可編程門陣列(FPGA)。FPGA已經被證明有能力處理各種不同的任務,從相對簡單的控制功能到更加復雜的算法操作。雖然FPGA在某些功能上比設計專用ASIC硬件具有時間和成本上的優勢,但在面向軟件應用中FPGA比傳統處理器和DSP的優勢并沒有體現出來。這很大程度上是由于過去割裂了硬件和軟件開發工具和方法之間的關系。 然而最近FPGA在面向軟件設計工具方面的發展,及器件容量的持續增

- 關鍵字:

FPGA/協處理器

協處理器介紹

協處理器

協處理器(coprocessor),一種芯片,用于減輕系統微處理器的特定處理任務。

目錄

1簡介

·特定處理任務

·內核相連

·擴展指令集

2超級CPU

·協處理器的消亡

·ARM 微處理器

1簡介

特定處理任務

例如,數學協處理器可以控制數字處理;圖形協處理器可以處理視頻繪制。例如,intel pentium [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473