- 簡易交通燈:本節將向您介紹Verilog語法之中的精髓內容——狀態機,并且將利用狀態機實現十字路口的交通燈。====硬件說明與實現項目框圖====上圖為十字路口交通示意圖分之路與主路,要求如下:交通燈主路上綠燈持續15s的時間,黃燈3s的時間,紅燈10s的時間;交通燈支路上綠燈持續7s的時間, 黃燈持續3秒的時間,紅燈18秒的時間;根據上述要求,狀態機設計框架分析如下:S1:主路綠燈點亮,支路紅燈點亮,持續15s的時間;S2:主路黃燈點亮,支路紅燈點亮,持續3s的時間;S3:主路紅燈點亮,支路綠燈點亮,持

- 關鍵字:

交通燈 狀態機 FPGA Lattice Diamond 小腳丫

- 簡易交通燈:本節將向您介紹Verilog語法之中的精髓內容——狀態機,并且將利用狀態機實現十字路口的交通燈。硬件說明與實現項目框圖上圖為十字路口交通示意圖分之路與主路,要求如下: * 交通燈主路上綠燈持續15s的時間,黃燈3s的時間,紅燈10s的時間; * 交通燈支路上綠燈持續7s的時間, 黃燈持續3秒的時間,紅燈18秒的時間;根據上述要求,狀態機設計框架分析如下: * S1:主路綠燈點亮,支路紅燈點亮,持續15s的時間; * S2:主路黃燈點亮,支路紅燈點亮,持續3s的時間; * S3:主路紅燈點亮,支

- 關鍵字:

交通燈 狀態機 FPGA Lattice Diamond 小腳丫

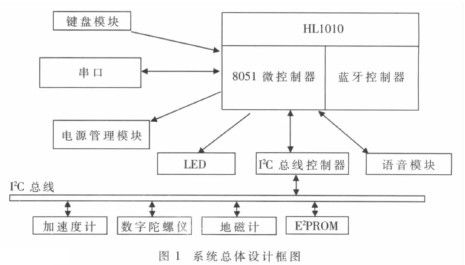

- 說到單片機編程,不得不說到狀態機,狀態機做為軟件編程的主要架構已經在各種語言中應用,當然包括C語言,在一個思路清晰而且高效的程序中,必然有狀態機的身影浮現。靈活的應用狀態機不僅是程序更高效,而且可讀性和擴展性也很好。狀態無處不在,狀態中有狀態,只要掌握了這種思維,讓它成為您編程中的一種習慣,相信您會受益匪淺。

- 關鍵字:

單片機 狀態機

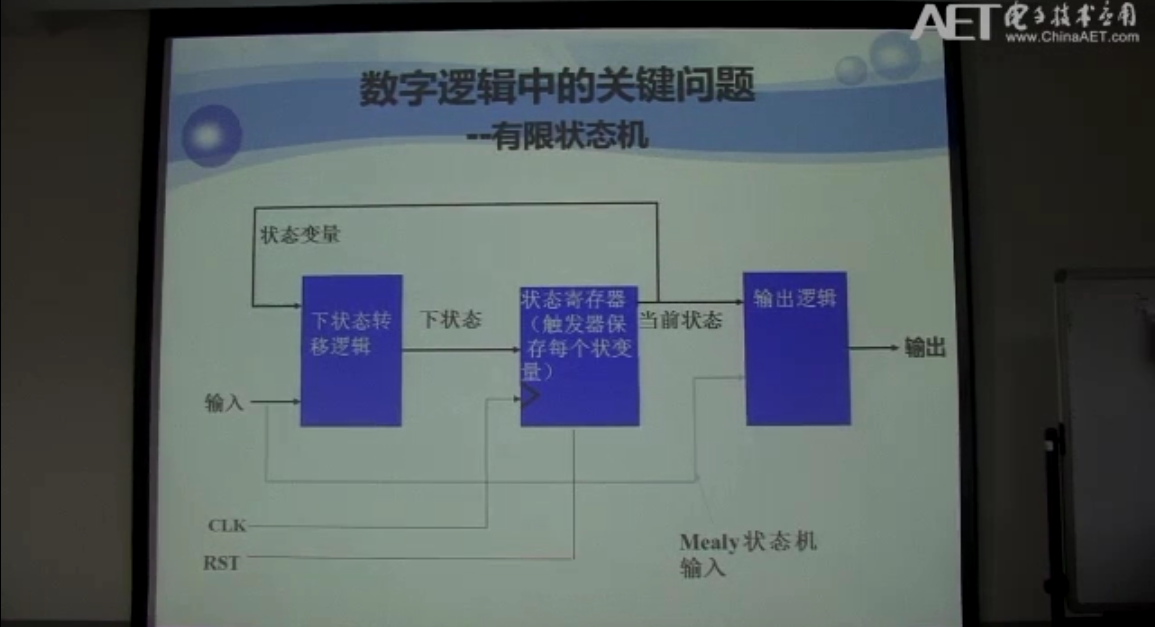

- FPGA工程師:如何在FPGA中實現狀態機?-安全高效的狀態機設計對于任何使用FPGA的工程師而言都是一項重要技能。選擇Moore狀態機、Mealy狀態機還是混合機取決于整個系統的需求。無論選擇哪種類型的狀態機,充分掌握實現方案所需的工具和技巧,將確保您實現最佳解決方案。本文主要介紹如何在FPGA中實現狀態機

- 關鍵字:

FPGA 狀態機 通信協議 控制器 FPGA教程

- 基于狀態機的LCD多級菜單設計方案-液晶顯示器由于其體積和功耗等因素,非常適合嵌入式環境的使用。近年來,隨著微處理器性能的提高,嵌入式系統實現的功能越來越強大,產生的數據量也越來越大。

- 關鍵字:

狀態機 LCD顯示 嵌入式系統

- 基于狀態機的電源控制器設計數字電源-數字電源可用于實現許多很有意思的功能。借助可編程調節環 路,可在不同工作條件下獲得更佳的環路特性。電源與完整系 統的數字連接可實現電壓和電流的精確監控。此外,數字電源還提供高靈活性。可以相當快的速度修改不同參數。這簡化了 電路設計過程并加快了系統衍生產品的開發。

- 關鍵字:

ADP1055 狀態機 數字電源 ADI

- 初學者對有限狀態機(FSM)的設計的認識-有限狀態機(FSM)是一種常見的電路,由時序電路和組合電路組成。設計有限狀態機的第一步是確定采用Moore狀態機還是采用Mealy狀態機。

- 關鍵字:

狀態機 FSM 有限狀態機

- 通過模塊之間的調用實現自頂向下的設計-通過模塊之間的調用實現自頂向下的設計目的:學習狀態機的嵌套使用實現層次化、結構化設計。

- 關鍵字:

模塊 狀態機

- 利用狀態機的狀態機實現層次結構化設計-練習九.利用狀態機的嵌套實現層次結構化設計目的:1.運用主狀態機與子狀態機產生層次化的邏輯設計;

- 關鍵字:

狀態機 FGPA

- 通過減少寄存器間的邏輯延時來提高工作頻率,或通過流水線設計來優化數據處理時的數據通路來滿足高速環境下FPGA或CPLD中的狀態機設計要求。本文給出了采用這些技術的高速環境狀態機設計的規范及分析方法和優化方法,并給出了相應的示例。

- 關鍵字:

狀態機

- 介紹在QUATUSII環境下,采用FPGA可編程邏輯器件開發的電子密碼鎖,并利用狀態機(FSM)實現鍵盤消抖及系統主控模塊的行為控制,從實際工程設計角度闡述了系統所有模塊及其工作原理、軟件設計方法,提出了系統設計注意要點。

- 關鍵字:

QUATUSII 密碼鎖 FPGA 狀態機

- 介紹了SDRAM的存儲體結構、主要控制時序和基本操作命令,并且結合實際系統,給出了一種用FPGA實現的通用SDRAM控制器的方案。

- 關鍵字:

VHDL 狀態機 SDRAM

- 在FPGA/CPLD設計中,狀態機是最典型、應用最廣泛的時序電路模塊,如何設計一個穩定可靠的狀態機是我們必須面對的問題.

- 關鍵字:

時序電路 狀態機 FPGA

- 狀態機設計是HDL設計里面的精華,幾乎所有的設計里面都或多或少地使用了狀態機的思想。狀態機,顧名思義,就是一系列狀態組成的一個循環機制,這樣的結構使得編程人員能夠更好地使用HDL語言,同時具有特定風格的狀態機也能提高程序的可讀性和調試性。

- 關鍵字:

VerilogHDL 狀態機 FPGA

- 狀態機性能的好壞對系統性能有較大的影響。良好的狀態機的實現不僅與狀態機的設計有關,而且與采用的綜合策略密切相關,不同的綜合策略對最終實現的狀態機的性能有很大的影響。

- 關鍵字:

狀態機 自動優化 邏輯控制

狀態機介紹

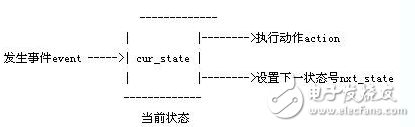

關于狀態機的一個極度確切的描述是它是一個有向圖形,由一組節點和一組相應的轉移函數組成。狀態機通過響應一系列事件而“運行”。每個事件都在屬于“當前” 節點的轉移函數的控制范圍內,其中函數的范圍是節點的一個子集。函數返回“下一個”(也許是同一個)節點。這些節點中至少有一個必須是終態。當到達終態, 狀態機停止。

包含一組狀態集(states)、一個起始狀態(start state)、一組輸入符號 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473