- 摘要 : 本文介紹了以ADAM-5510KW為監控核心的青藏鐵路旅客用列車真空集便監控系統的實現與應用,以及Modbus RTU協議在此系統中的典型應用。由臺灣研華公司推出的PC-Based軟邏輯控制器ADAM-5510KW系列產品,符合IEC

- 關鍵字:

監控系統 應用 真空 列車 邏輯 控制器 基于

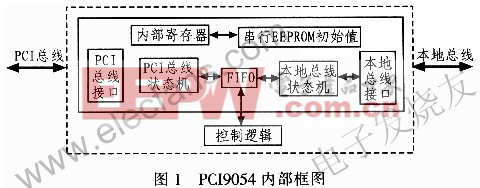

- PCI總線支持突發傳送,多處理器和并發工作,廣泛應用于各種平臺設計。基于PCI9054的接口板也廣泛地應用于各種高速、大數據量的處理系統。由于PCI9054橋接有PCI總線和本地總線,開發者不必過多考慮復雜的PCI總線規

- 關鍵字:

邏輯 設計 接口 數據傳輸 PCI9054 路器 基于

- 摘要:針對1553B 總線協議控制器基本依賴于進口專用芯片現狀,提出了以Xilinx 公司Virtex-II Pro FPGA 為核心實現1553B 總線接口邏輯的系統設計方案。采用SOPC 技術,將PowerPC 405 硬核處理器與總線接口邏輯集成

- 關鍵字:

邏輯 設計 接口 總線 SOPC 1553B 基于

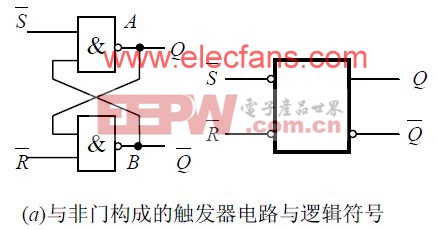

- 基本觸發器的邏輯結構如圖13-1所示。它可由兩個與非門交叉耦合構成,圖13-1(a)是其邏輯電路圖和邏輯符號,也可以由兩個或非門交叉耦合構成,如圖13-1(b)所示。圖13-1 基本觸發器邏輯結構及邏輯符號現在以兩個與非門組

- 關鍵字:

工作 原理 結構 邏輯 觸發器 基本

- 在數學上,我們有三種描述函數的方法:公式、表格和圖形。同樣,我們有三種描述觸發器邏輯功能的方法,一是特性方程,二是特性表,三是狀態轉換圖【圖4.3.1,4.3.2, 4.3. 3,4.3.4】

- 關鍵字:

觸發器 邏輯 函數描述 方法

- 基于絕熱開關理論的能量回收邏輯與傳統的靜態CM0s邏輯相比,能夠大大減少電路的功率消耗。這里介紹了一種使用單相正弦電源時鐘的能量回收邏輯,分別用靜態CMOS邏輯和這種能量回收邏輯設計,并仿真了一個兩位乘法器電路,比較了這兩種電路的性能。研究表明,采用能量回收邏輯設計的乘法器顯著降低了電路的功率消耗。

- 關鍵字:

電路設計 法器 功耗 邏輯 基于

- 介紹了基于MSI可編程計數器74Lsl61的時序邏輯電路設計技術,目的是探索MSI可編程計數器實現一般時序邏輯電路的擴展應用方法,即以計數器Q3,Q2,Q1,Q0端的代碼組合表示時序邏輯電路的各個狀態,由輸入變量控制計數器的EP,ET及端,綜合利用計數、置數、保持功能,使計數器的狀態變化滿足所要求的時序,用計數功能實現“次態=現態+1”的二進制時序關系,用置數功能實現“次態=預置數”的非二進制時序關系,用保持功能實現“次態=現態”的自循環時序關系。所述方法的創新點是提出了MSI可編程計數器改變應用方向的邏

- 關鍵字:

邏輯 電路設計 時序 計數器 可編程 基于

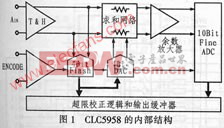

- 采用可編程邏輯器件和A/D轉換器的高速數據采集卡的設計方案, 用于PC的采集系統以前大多有用ISA總線結構,這種結構的最大缺點是傳輸速率低,無法實現高速數據的實時傳輸。而PCI總線則以其卓越的性能受到了廣泛的應用。32位PCI總線的最大傳輸數據速率可達132MB/s,64位PCI總線的

- 關鍵字:

高速 數據采集 設計 方案 轉換器 A/D 可編程 邏輯 器件

- 邏輯和DRAM技術跨產業合作大戲正式登場,聯電、爾必達(Elpida)攜手開發TSV技術的簽約儀式將于21日召開記者會對外宣布;值得注意的是,業界透露,雙方技術合作僅是第1階段,未來第2階段考慮以交叉持股的方式,讓雙方的合作關系更為緊密,因此聯電為引進策略聯盟伙伴而辦理的私募案,爾必達將是口袋人選之一。

聯電、爾必達和力成將于今日針對TSV技術舉行簽約儀式,這是近年來邏輯和存儲器技術領域罕見的跨產業大合作,爾必達(Elpida)社長坂本幸雄過去是聯日半導體(UMCj)的總經理,因此爾必達與聯電雙

- 關鍵字:

Elpida DRAM 邏輯

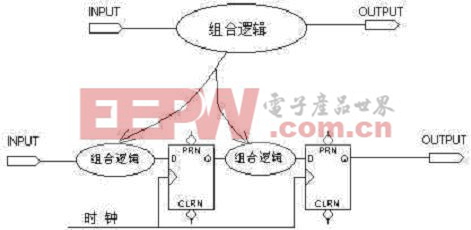

- 實現拆分大組合邏輯的方法,圖1是很多為了提高系統時鐘采用的拆分大組合邏輯的方法,但是沒有提供具體如何拆分的實例。我覺得實例才是重要的。但我不明白在寫代碼時,如何知道這樣寫會被綜合成一個很大的邏輯,一些簡單的可以想到(比如大的計數

- 關鍵字:

方法 邏輯 組合 拆分 實現

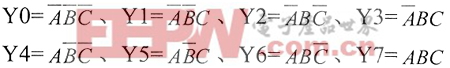

- 采用表格法化簡邏輯函數技術,1、概述在設計邏輯電路圖時,由真值表直接得到的函數往往比較復雜。代數法和卡諾圖法等方法對于變量數目較多的邏輯函數則效果不佳,本文介紹一種可以化簡復雜邏輯函數的方法──表格法,該方法可以對變量數目較多的邏

- 關鍵字:

技術 函數 邏輯 表格 采用

- 數字邏輯電路教學中的C語言描述和應用,摘要:為了改進數字邏輯電路教學方法以適應電子技術迅猛發展的需要,我們探索和實踐了數字邏輯電路教學的新方法,這就是基于計算機高級語言(C語言)的數字邏輯電路課堂教學和實驗教學方法,本文重點介紹了本教學方法

- 關鍵字:

描述 應用 語言 教學 邏輯 電路 數字

- 本文將探討在混合電壓供電的移動設計中,混合電壓電平如何提高ICC電源電流及邏輯門如何降低功耗。當前的移動設計在努力在高耗能(power-rich)的功能性和更長電池壽命的需求之間取得平衡。 目前,大多數便攜設備都備有

- 關鍵字:

技術 方法 邏輯 功耗 移動 設計 降低

- 基于Verilog的順序狀態邏輯FSM的設計與仿真, 硬件描述語言Verilog為數字系統設計人員提供了一種在廣泛抽象層次上描述數字系統的方式,同時,為計算機輔助設計工具在工程設計中的應用提供了方法。該語言支持早期的行為結構設計的概念,以及其后層次化結構設計的

- 關鍵字:

FSM 設計 仿真 邏輯 狀態 Verilog 順序 基于

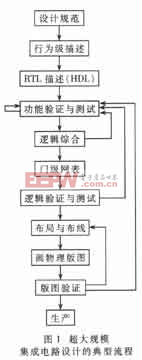

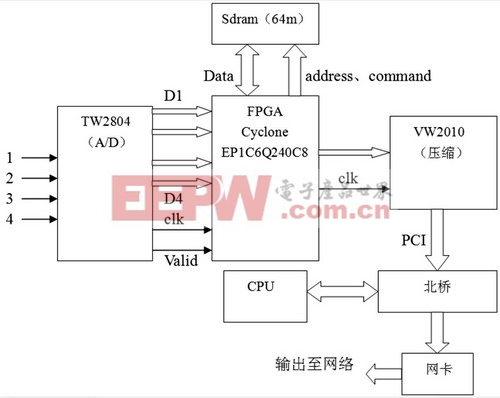

- 摘要:本文主要介紹在視頻監控板中多路視頻信號輸入情況下的數據緩存、信號格式轉換的設計,并用Altera的Cyclone器件實現的整個過程。包括簡單介紹視頻監控器電路板的原理,此轉接邏輯在系統中的作用和地位,并詳細

- 關鍵字:

邏輯 設計 轉接 視頻監控 網絡 數字

邏輯介紹

您好,目前還沒有人創建詞條邏輯!

歡迎您創建該詞條,闡述對邏輯的理解,并與今后在此搜索邏輯的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473