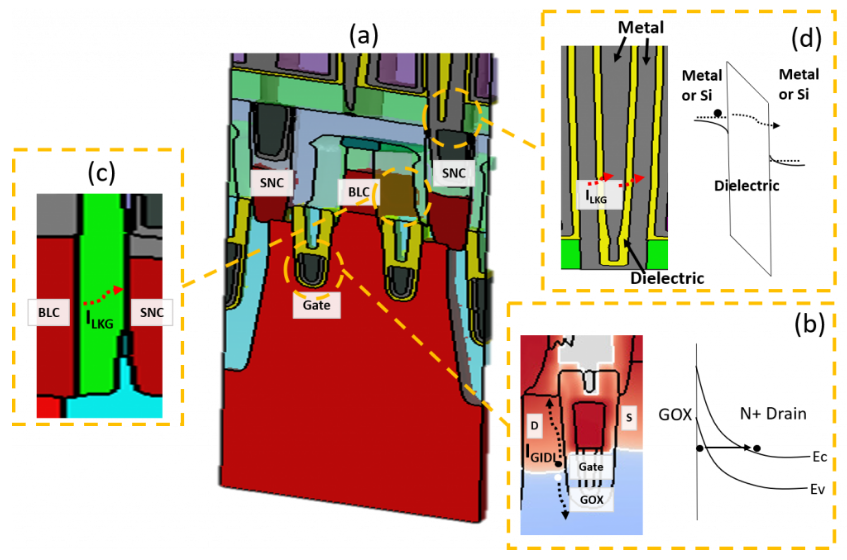

- 從20nm技術節點開始,漏電流一直都是動態隨機存取存儲器(DRAM)設計中引起器件故障的主要原因。即使底層器件未出現明顯的結構異常,DRAM設計中漏電流造成的問題也會導致可靠性下降。漏電流已成為DRAM器件設計中至關重要的一個考慮因素。圖1. (a) DRAM存儲單元;(b)單元晶體管中的柵誘導漏極泄漏電流 (GIDL);(c)位線接觸 (BLC) 與存儲節點接觸 (SNC) 之間的電介質泄漏;(d) DRAM電容處的電介質泄漏。DRAM存儲單元(圖1 (a))在電

- 關鍵字:

DRAM GIDL

gidl介紹

您好,目前還沒有人創建詞條gidl!

歡迎您創建該詞條,闡述對gidl的理解,并與今后在此搜索gidl的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473