asic-to-fpga 文章 最新資訊

7種LED點陣顯示屏及其控制系統(tǒng)的設(shè)計與實現(xiàn)

- LED點陣顯示屏是集微電子技術(shù)、計算機技術(shù)、信息處理技術(shù)于一體的大型顯示屏系統(tǒng)。它以其色彩鮮艷,動態(tài)范圍廣,亮度高,壽命長,工作穩(wěn)定可靠等優(yōu)點而成為眾多顯示媒體以及戶外作業(yè)顯示的理想選擇。目前,已經(jīng)被廣泛應(yīng)用到軍事、車站、賓館、體育、新聞、金融、證券、廣告以及交通運輸?shù)仍S多行業(yè)。

- 關(guān)鍵字: LED點陣 控制系統(tǒng) 發(fā)光管 FPGA CPLD

基于FPGA的RFID讀卡器的完整設(shè)計

- RFID(無線射頻識別)技術(shù),又稱為電子標簽或者無線標簽識別,是一種利用無線射頻通信實現(xiàn)的非接觸式自動識別技術(shù),被列為21世紀最有前途的重要產(chǎn)業(yè)和應(yīng)用技術(shù)之一。

- 關(guān)鍵字: RFID V2pro FPGA 射頻設(shè)別技術(shù)

基于FPGA的通用網(wǎng)絡(luò)數(shù)據(jù)采集控制器方案

- 開發(fā)一款通用性強的網(wǎng)絡(luò)數(shù)據(jù)采集控制器,適合PC(windows與Unix、Linux系統(tǒng))與片上系統(tǒng)之間的通信(片上運行軟核或硬核嵌入式系統(tǒng)) ,提取的資源是本地控制器參數(shù)(如PID參數(shù)、射頻信號幅度相位信息和誤差因子等)。

- 關(guān)鍵字: MicroBlaze 采集控制器 FPGA

經(jīng)典款嵌入式智能小車的設(shè)計技巧,提供硬件選型

- 傳統(tǒng)智能小車,特別是嵌入式系統(tǒng),一般都是基于單片機或者ARM的嵌入式系統(tǒng),基本上都由軟件系統(tǒng)和硬件系統(tǒng)組成的,硬件系統(tǒng)方面,跟傳統(tǒng)的搭建硬件環(huán)境一樣,只能做相對裁剪和功能拓展,但是,本項目的課題是通過xilinx的FPGA開發(fā)板搭建嵌入式的硬件環(huán)境,從最小系統(tǒng)到IP核的添加,都是根據(jù)需要進行拓展的,實現(xiàn)一對一的拓展,不浪費資源,而且基于F

- 關(guān)鍵字: 智能小車 Spartan-6 FPGA 電源穩(wěn)壓芯片 全橋驅(qū)動

嵌入式安全保密模塊的設(shè)計及在軟件版權(quán)保護中的應(yīng)用

- 本項目設(shè)計方案是基于FPGA的嵌入式安全保密模塊ESMF (Embedded Security Module based on FPGA),并通過高密計算返回安全認證碼,通過安全認證碼與密匙校驗,為用戶解決高密數(shù)據(jù)存儲、身份認證等很多安全問題,這將為軟件版權(quán)的保護提供有效的途徑。

- 關(guān)鍵字: 嵌入式安全保密模塊 軟件版權(quán)保護 FPGA ESMF

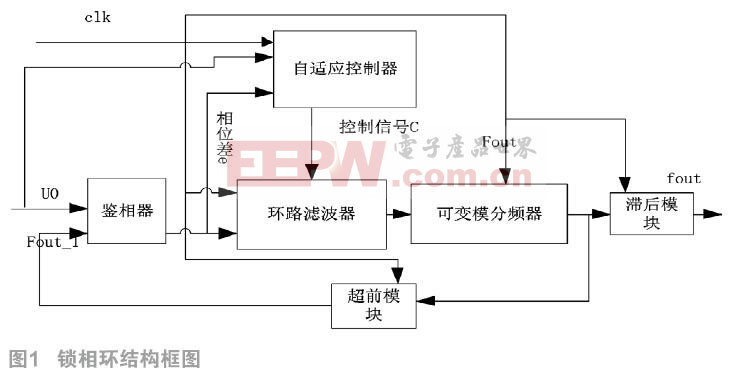

自變模無線電能傳輸全數(shù)字鎖相環(huán)

- 針對無線電能傳輸頻率跟蹤設(shè)計中傳統(tǒng)鎖相環(huán)電路設(shè)計復雜、跟蹤速度慢、鎖相頻帶窄和無超前滯后環(huán)節(jié),單獨模塊設(shè)計修改繁瑣等問題,對自變模全數(shù)字鎖相環(huán)進行改進, 與傳統(tǒng)的全數(shù)字鎖相環(huán)相比,該鎖相環(huán)采用可變模分頻器,使得中心頻率可變,鎖相范圍增大;通過前饋回路進行鑒頻調(diào)頻,提高了鎖相速度;同時,其環(huán)路濾波器采用比例積分結(jié)構(gòu),使得鎖相輸出無靜差且比例積分參數(shù)依據(jù)相位差自動進行調(diào)節(jié);通過參數(shù)設(shè)置可調(diào)節(jié)輸出信號的相位。應(yīng)用modelsim進行仿真,并進行實物驗證證實了該設(shè)計具有寬范圍的鎖相能力及快速精確的頻率跟蹤性能。

- 關(guān)鍵字: 全數(shù)字鎖相環(huán) 比例積分控制 FPGA 無線電能傳輸 201706

基于FPGA助力高端存儲器接口設(shè)計

- 高性能系統(tǒng)設(shè)計師在滿足關(guān)鍵時序余量的同時要力爭獲得更高性能,而存儲器接口設(shè)計則是一項艱巨挑戰(zhàn)。雙倍數(shù)據(jù)速率SDRAM和4倍數(shù)據(jù)速率SDRAM都采用源同步接口來把數(shù)據(jù)和時鐘(或選通脈沖)由發(fā)射器傳送到接收器。接收器接口內(nèi)部利用時鐘來鎖存數(shù)據(jù),此舉可消除接口控制問題(例如在存儲器和FPGA間的信號傳遞時間),但也為設(shè)計師帶來了必須解決的新挑戰(zhàn)。 關(guān)鍵問題之一就是如何滿足各種讀取數(shù)據(jù)捕捉需求以實現(xiàn)高速接口。隨著數(shù)據(jù)有效窗越來越小,該問題也益發(fā)重要;同時,更具挑戰(zhàn)性的問題是,如何讓接收到的時鐘與數(shù)據(jù)中心對準

- 關(guān)鍵字: FPGA 存儲器

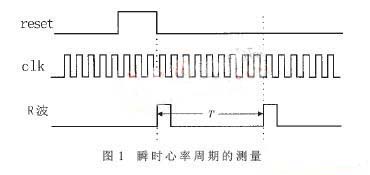

FPGA在數(shù)字式心率計中的電路組成及工作原理

- 心率計是常用的醫(yī)學檢查設(shè)備,實時準確的心率測量在病人監(jiān)控、臨床治療及體育競賽等方面都有著廣泛的應(yīng)用。心率測量包括瞬時心率測量和平均心率測量。瞬時心率不僅能夠反映心率的快慢。同時能反映心率是否勻齊;平均心率雖只能反映心率的快慢,但記錄方便,因此這兩個參數(shù)在測量時都是必要的。 測量心率有模擬和數(shù)字兩種方法。模擬方法是在給定的時間間隔內(nèi)計算R波(或脈搏波)的脈沖個數(shù),然后將脈沖計數(shù)乘以一個適當?shù)某?shù)測量心率的。這種方法的缺點是測量誤差較大、元件參數(shù)調(diào)試困難、可靠性差。數(shù)字方法是先測量相鄰R波之間的時間,再

- 關(guān)鍵字: FPGA 分頻

ASIC設(shè)計中不可忽視的幾大問題

- ASIC的復雜性不斷提高,同時工藝在不斷地改進,如何在較短的時間內(nèi)開發(fā)一個穩(wěn)定的可重用的ASIC芯片的設(shè)計,并且一次性流片成功,這需要一個成熟的ASIC的設(shè)計方法和開發(fā)流程。 本文結(jié)合NCverilog,DesignCompile,Astro等ASIC設(shè)計所用到的EDA軟件,從工藝獨立性、系統(tǒng)的穩(wěn)定性、復雜性的角度對比各種ASIC的設(shè)計方法,介紹了在編碼設(shè)計、綜合設(shè)計、靜態(tài)時序分析和時序仿真等階段經(jīng)常忽視的問題以及避免的辦法,從而使得整個設(shè)計具有可控性。

- 關(guān)鍵字: ASIC

asic-to-fpga介紹

您好,目前還沒有人創(chuàng)建詞條asic-to-fpga!

歡迎您創(chuàng)建該詞條,闡述對asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。 創(chuàng)建詞條

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司