asic-to-fpga 文章 最新資訊

基于FPGA的步進(jìn)電機(jī)優(yōu)化控制

- 摘要:隨著控制技術(shù)以及步進(jìn)電機(jī)(Stepper Motor)的發(fā)展,現(xiàn)代工業(yè)的許多領(lǐng)域?qū)Σ竭M(jìn)電機(jī)的需求也越來越大。但是傳統(tǒng)的步進(jìn)電機(jī)控制系統(tǒng)多以單片機(jī)等微處理器為基礎(chǔ),往往具有控制電路體積大、控制效率低、穩(wěn)定性差等

- 關(guān)鍵字: 步進(jìn)電機(jī) 控制系統(tǒng) FPGA 細(xì)分原理 PWM控制技術(shù)

基于STM32和FPGA的CAN總線運(yùn)動(dòng)控制器的設(shè)計(jì)

- 運(yùn)用低功耗COrtex—M3微控制器STM32F103VBT6和FPGA芯片設(shè)計(jì)一種基于CAN總線的運(yùn)動(dòng)控制器。介紹系統(tǒng)的體系結(jié)構(gòu)、主要硬件設(shè)計(jì)和軟件結(jié)構(gòu)。利用FPGA高速處理能力實(shí)現(xiàn)控制算法,與外界通信采用STM32和CAN總線技術(shù),系統(tǒng)穩(wěn)定可靠,另外,將設(shè)計(jì)好的FPGA程序或是C程序進(jìn)行封裝,系統(tǒng)的可移植性強(qiáng)。

- 關(guān)鍵字: STM32 FPGA CAN總線 運(yùn)動(dòng)控制

基于雙麥克風(fēng)聲源定位的視頻跟蹤

- 摘要:聲源定位跟蹤技術(shù)在當(dāng)今社會(huì)有著越來越廣泛的應(yīng)用。在此使用兩個(gè)高靈敏度麥克風(fēng)作為傳感器,配以音頻信號(hào)處理芯片,接收音頻信號(hào)并進(jìn)行模數(shù)轉(zhuǎn)換,使用FPGA器件作為核心控制器,結(jié)合TDOA算法和ILD算法,實(shí)現(xiàn)在室

- 關(guān)鍵字: 雙麥克風(fēng) 聲源定位 FPGA NiosⅡ

嵌入式系統(tǒng)的自適應(yīng)前照燈系統(tǒng)設(shè)計(jì)

- 摘要:為了改善駕駛員在夜間或能見度較低環(huán)境下的視野范圍,提高行駛的安全性,介紹了一種基于嵌入式系統(tǒng)的汽車自適應(yīng)前照燈系統(tǒng)的設(shè)計(jì)方案。此系統(tǒng)中的前照燈控制器采用FPGA來控制CAN總線控制器、數(shù)/模轉(zhuǎn)換器和全橋

- 關(guān)鍵字: 步進(jìn)電機(jī) FPGA MCP2510 LMD18245

基于FPGA的多路視頻收發(fā)系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

- 摘要:為了實(shí)現(xiàn)對(duì)多路視頻和數(shù)據(jù)信號(hào)的同步傳輸,提出了一種基于FPGA的視頻數(shù)據(jù)綜合傳輸系統(tǒng)設(shè)計(jì)方案,并完成系統(tǒng)的軟硬件設(shè)計(jì)。該系統(tǒng)的硬件部分主要由FPGA、CPLD芯片及光模塊等設(shè)備組成,軟件部分采用VHDL語言進(jìn)行

- 關(guān)鍵字: 視頻傳輸 FPGA 數(shù)據(jù)傳輸 光模塊

智原發(fā)表PowerSlash(TM)硅智財(cái)于聯(lián)電55奈米超低功耗製程支援物聯(lián)網(wǎng)應(yīng)用開發(fā)

- 聯(lián)華電子今(12日)與ASIC設(shè)計(jì)服務(wù)暨IP研發(fā)銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)共同發(fā)表智原科技于聯(lián)電55奈米超低功耗製程(55ULP)的PowerSlash™基礎(chǔ)IP方案。智原PowerSlash™與聯(lián)電製程技術(shù)相互結(jié)合設(shè)計(jì),為超低功耗的無線應(yīng)用需求技術(shù)進(jìn)行優(yōu)化,滿足無線物聯(lián)網(wǎng)產(chǎn)品的電池長期壽命需求。 智原科技行銷暨投資副總于德旬表示:「物聯(lián)網(wǎng)應(yīng)用建構(gòu)過程中,效能往往受制于低功耗技術(shù)。而今透過聯(lián)電55奈

- 關(guān)鍵字: 聯(lián)華電子 ASIC

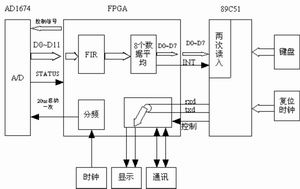

FPGA實(shí)現(xiàn)的FIR算法在汽車動(dòng)態(tài)稱重儀中的應(yīng)用

- 引言 車輛在動(dòng)態(tài)稱重時(shí),作用在平臺(tái)上的力除真實(shí)軸重外,還有許多因素產(chǎn)生的干擾力,如:車速、車輛自身諧振、路面激勵(lì)、輪胎驅(qū)動(dòng)力等,給動(dòng)態(tài)稱重實(shí)現(xiàn)高精度測(cè)量造成很大困難。若在消除干擾的過程中采用模擬方法濾波,參數(shù)則不能過大,否則將產(chǎn)生過大的延遲導(dǎo)致不能實(shí)現(xiàn)實(shí)時(shí)處理,從而造成濾波后的信號(hào)仍然含有相當(dāng)一部分的噪聲。所以必須采用數(shù)字濾波消除干擾。 FIR濾波的原理及實(shí)現(xiàn) 本文采用FIR數(shù)字濾波,其原理如公式1所示。 Y(n)= (1) 其中h(k)為系統(tǒng)濾波參數(shù),x(n)為采集的信

- 關(guān)鍵字: FPGA FIR

基于USB2.0協(xié)議的通用測(cè)控通信接口設(shè)計(jì)

- 隨著我國航空航天技術(shù)的迅速發(fā)展,對(duì)地面遙控遙測(cè)接收機(jī)的實(shí)時(shí)性和高速數(shù)據(jù)傳輸性能的要求越來越高。越來越多的遙測(cè)遙控地面信道處理器都采用了實(shí)時(shí)能力更強(qiáng)的高速DSP/FPGA架構(gòu)設(shè)計(jì)方案。基于DSP/FPGA架構(gòu)的設(shè)計(jì)方案

- 關(guān)鍵字: CY7C68013A 測(cè)控通信 FPGA USB固件設(shè)計(jì)

基于雙口RAM核監(jiān)測(cè)數(shù)字示波器設(shè)計(jì)研究

- 摘要:在核監(jiān)測(cè)中,常將各種傳感器輸出的信號(hào)通過A/D轉(zhuǎn)換器轉(zhuǎn)換為數(shù)字信號(hào),然后利用數(shù)字信號(hào)處理技術(shù)對(duì)各種核信號(hào)進(jìn)行數(shù)字處理。為了準(zhǔn)確測(cè)量核信號(hào)數(shù)字波形的各種參數(shù),對(duì)基于FPGA雙口RAM的數(shù)字示波器進(jìn)行了設(shè)計(jì)和

- 關(guān)鍵字: 核脈沖 數(shù)字示波器 數(shù)字波形 FPGA 雙口RAM

asic-to-fpga介紹

您好,目前還沒有人創(chuàng)建詞條asic-to-fpga!

歡迎您創(chuàng)建該詞條,闡述對(duì)asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。 創(chuàng)建詞條

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司