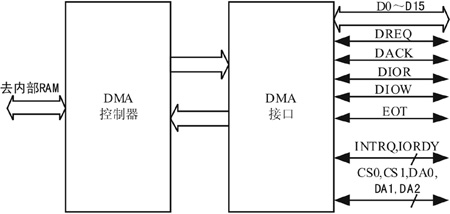

- 直接存儲器存取方式不僅具有高速度、高效率的特點,而且CPU資源占用少,因此在需要高速、批量交換數據的場合得到了廣泛的應用。在DOS下編寫DMA控制程序并不難,但要編制出精美實用的界面則是一件非常繁瑣的工作,而且效果

- 關鍵字:

Windows DMA 98 平臺開發

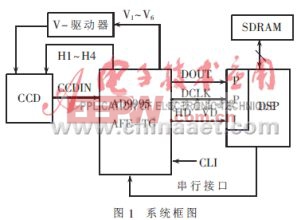

- 介紹了換體DMA高速數據采集電路原理及其CPLD實現。用CPLD設計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積大、電路復雜、不能實現在線升級等問題,大大提高了系統的整體性能。

- 關鍵字:

CPLD DMA 高速數據 采集電路

- 摘要:在USB接口和USB外設之間使用DMA方式傳輸數據,大大提高了USB傳輸數據的吞吐量。本文介紹了基于ISP1581USB接口芯片的DMA傳輸應用。

關鍵詞:ISP1581;USB2.0;DMA控制器;固件

引言

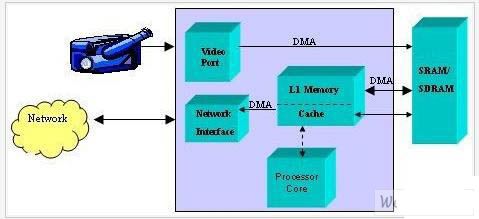

隨著USB2.0規范的推出,USB總線的最高數據傳輸速率可達到480Mbit/s,這進一步延伸了它的使用范圍,越來越多的設計者在設計嵌入式系統或者計算機外圍設備時開始采用USB總線進行數據傳輸,為了保證高的數據傳輸速率,許多USB接口芯片提供了直接存儲器存取(DMA)方式,通過使用

- 關鍵字:

DMA ISP1581 200810

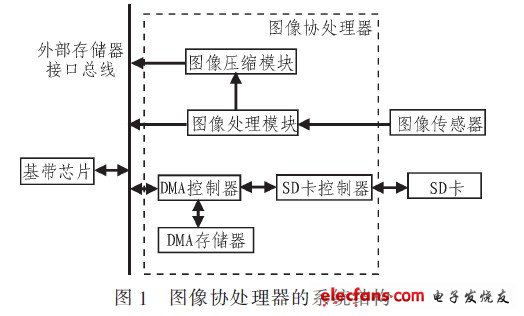

- 摘 要:采用OV2610的CMOS圖像傳感器和26K色的TFT液晶屏,在SOPC上集成了OV2610、TFT液晶控制器和DMA控制器,實現了圖像數據流的采集和顯示。

關鍵詞:DMA Avalon數據流模式 SDRAM

隨著大規模集成電路設計技術的進步、制造工藝水平的提高以及單個芯片上的邏輯門數的增加,嵌入式系統設計變得日益復雜。把整個系統集成到一個芯片上,即片上系統SoC(System on Chip)技術是當前嵌入式系統設計的一個研究熱點。在Altera公司提供的

- 關鍵字:

SoC DMA Avalon數據流模式 SDRAM

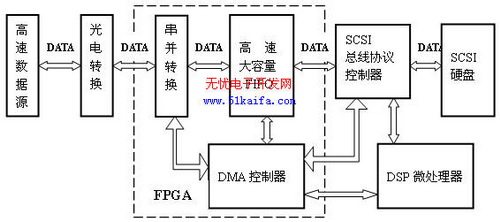

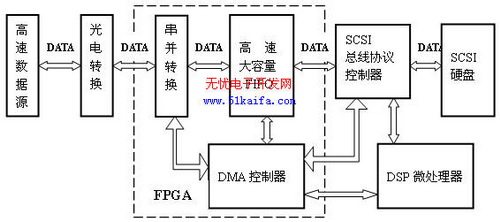

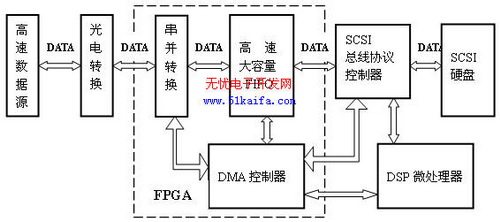

- 在持續數據采集存儲系統中,數據存儲是一項關鍵技術。常規的數據記錄器多采用總線型設計思路。過去的做法是通過內存將采集和存儲聯系起來。外部采集到的數據經由PCI總線送入系統內存,然后再由主機把數據寫入磁介質存儲器。由于數據兩次經由PCI總線進出內存,總線效率降低一半,速度也降低很多。

隨著對PCI總線和SCSI總線接口協議以及計算機系統結構的了解愈加深入,現在多采用映射內存及總線主控技術,使SCSI適配器對PCI采集設備直接進行訪問。由于避開了系統內存這一環節,速度得到了很大的提高。

- 關鍵字:

數據采集 存儲 PCI SCSI DMA DSP

- 在持續數據采集存儲系統中,數據存儲是一項關鍵技術。常規的數據記錄器多采用總線型設計思路。過去的做法是通過內存將采集和存儲聯系起來。外部采集到的數據經由PCI總線送入系統內存,然后再由主機把數據寫入磁介質存儲器。由于數據兩次經由PCI總線進出內存,總線效率降低一半,速度也降低很多。

隨著對PCI總線和SCSI總線接口協議以及計算機系統結構的了解愈加深入,現在多采用映射內存及總線主控技術,使SCSI適配器對PCI采集設備直接進行訪問。由于避開了系統內存這一環節,速度得到了很大的提高。

- 關鍵字:

數據采集 存儲 PCI SCSI DMA DSP

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

DSP DMA 操作 無阻塞請求 實現

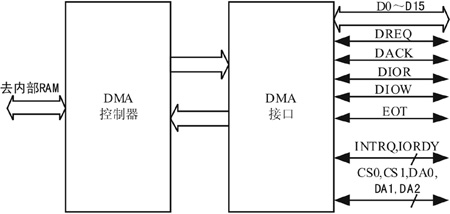

- 隨著科學技術的發展,計算機在測量與控制中的應用日益廣泛。為了使外部世界的模擬信號與計算機接口,需要進行模/數轉換,該轉換一般通過A/D芯片來完成。目前市場上出現了各種A/D芯片,且各種A/D芯片具有不同的控制方式和應用條件。對于高速數據采集,最大采樣頻率取決于A/D的轉換時間以及數據的傳輸時間。提高最大采樣頻率可通過縮短A/D的轉換時間或提高數據的傳輸速度來實現。如果與PC機接口,數據的傳輸速度決定于PC機的主頻以及數據的傳輸方式,常用的有查詢和中斷方式,若采用DMA傳輸方式則可進一步提高數據的傳輸速

- 關鍵字:

芯片 數據采集 電路 DMA

- 光盤拷貝機通常由一臺CD-ROM驅動器、數臺CD-R或CD-RW刻錄機和一個拷貝控制器組成。拷貝控制器首先從CD-ROM驅動器中讀出源盤數據,然后將數據流分多路傳輸到各個刻錄機,控制所有的刻錄機同步刻錄CD-R光盤。目前市場上的光盤拷貝機主要有聯機拷貝機、脫機拷貝機和自動拷貝機三種類型。

(1)聯機拷貝機

聯機光盤拷貝機由一臺通用PC機和一個裝有SCSI接口刻錄機的塔式機箱組成,塔箱與PC機之間用SCSI電纜相連。聯機拷貝機使用PC機作為光盤拷貝機控制器,并利用專門的CD-R拷貝軟件將刻錄

- 關鍵字:

FPGA 數字拷貝機 CPLD CPU DMA

- 0 引言

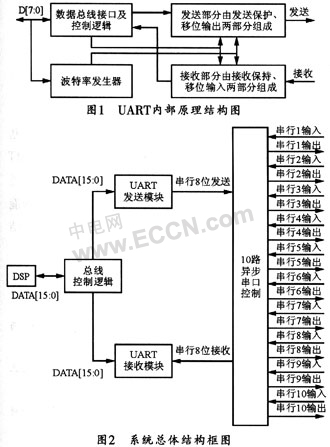

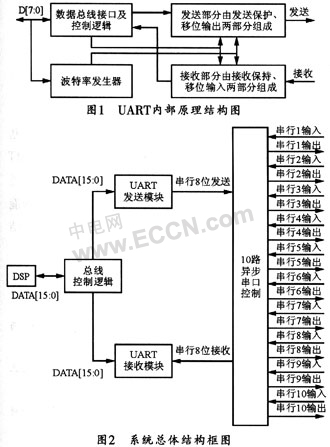

目前,在數字信號處理技術中,DSP+CPLD是控制接口設計中比較常用的方式。然而,AD-SP-BF533雖有異步串口,但該芯片只有一個異步串口,當一個系統中出現多個UART接口時,ADSP-BF533就顯得無能為力了。為此,本文采用CPLD來實現多路UART接口的設計,以滿足ADSP-BF533與多路UART接口的通信。

1 ADSP-BF533簡介

ADSP-BF533處理器是Blackfin系列產品中的一員。其最大工作頻率可達600 MHz。Blackfin處理器內核包

- 關鍵字:

DSP CPLD UART 接口電路 處理器 DMA

- 引言

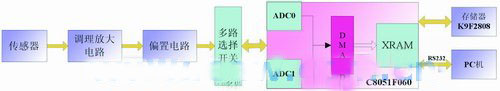

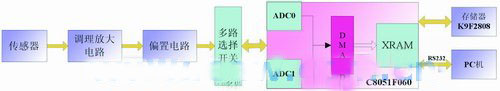

從上個世紀九十年代起,電子技術在鉆井井下得到應用。但井下鉆具的振動會給很多傳感器帶來不利影響。

特別是對測量井下鉆頭姿態的慣性導航傳感器影響巨大,在隨鉆振動環境中,如果對信號不作處理,根本就不能測量出正確的井斜角和方位角,也就無法實現井眼軌跡隨鉆控制的要求。本文介紹應用SoC芯片中的DMA技術對振動的高速采集和存儲功能的實現方法,并給出了鉆井環境中測試的結果。

方法的提出

傳統的數據采集方法采用CPU直接控制的方式進行數據采集,數據傳送需要經過CPU的中轉才能存入存儲器,

- 關鍵字:

SoC DMA 傳感器 CPU ADC

- 引言

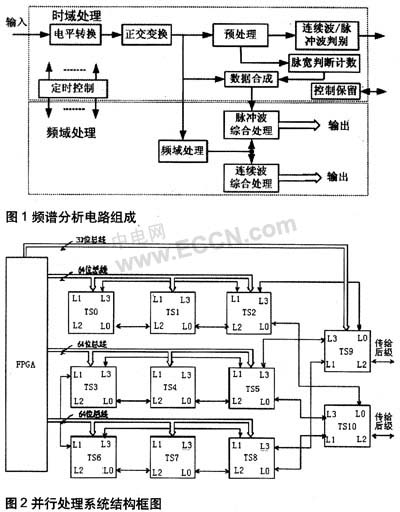

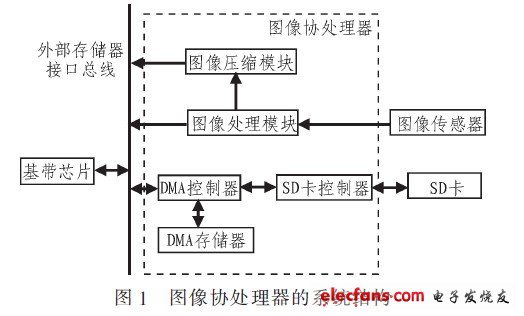

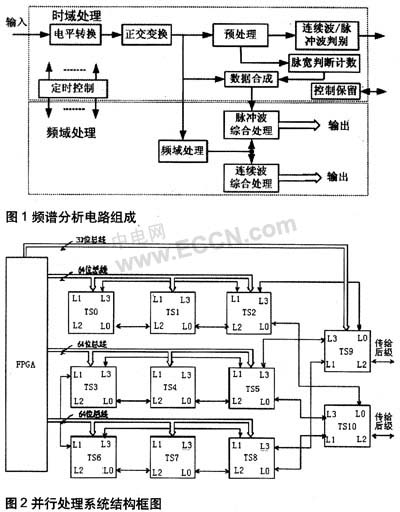

近年來,實時信號處理的要求越來越高,所用系統要求具有處理大量數據的能力,這就要求系統硬件要達到很高的運算速度,并且軟件處理程序也要盡可能優化,以保證系統的實時性。本文基于FPGA和ADSP-TS101S所實現的一種高速數據并行處理系統,可以進行實時連續波和脈沖波的處理,并將連續波的頻譜和脈沖波脈沖幅度信息、脈前時刻、脈寬及載頻打包輸出。整個系統的輸出延時被控制在1ms之內。

系統任務及系統結構

系統任務

系統頻譜分析電路組成結構如圖1所示。前端輸入為高頻寬帶模擬信號經過數

- 關鍵字:

FPGA DSP 信號處理 DMAR DMA

block dma介紹

您好,目前還沒有人創建詞條block dma!

歡迎您創建該詞條,闡述對block dma的理解,并與今后在此搜索block dma的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473