- 信號發生器又稱為波形發生器是一種常用的信號源并且廣泛應用于電子電路、通信、控制和教學實驗等領域的重要儀器之一。為了降低傳統函數信號發生器成本,改善信號發生器低頻穩定性。筆者結合FPGA和51單片機產生0.596 Hz頻率精度函數信號。筆者設計通過51單片機控制函數信號類型以及相關參數,用戶可通過按鍵設置需要的波形、波形幅度、波形頻率以及方波的占空比、相位。本文設計方案不僅具有良好的經濟前景,也可以為當代高等教育深化改革做一個參考方向。

1 系統設計方案

1.1 系統硬件設計

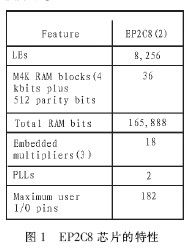

本文中設

- 關鍵字:

FPGA 51單片機

- 7.3 ModelSim的仿真流程

7.3.1 ModelSim的安裝

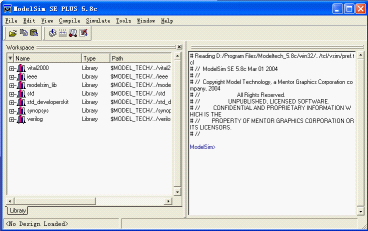

ModelSim的最新版本可以從互連網上免費得到,需要購買的只是License文件。ModelSim的下載地址為http://www.model.com/。打開網站頁面后可以點擊Download,用戶填寫完一張表格以后可以得到一個小時的下載時間。

獲得License的方法有很多種。

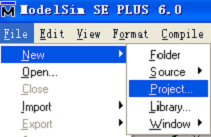

首先可以在線申請License文件,選取“開始→程序→ModelSim SE 5.8c&rar

- 關鍵字:

FPGA ModelSim

- 7.2 ModelSim仿真工具簡介

ModelSim是Model Technology(Mentor Graphics的子公司)的DHL硬件描述語言的仿真軟件,該軟件可以用來實現對設計的VHDL、Verilog或者是兩種語言混合的程序進行仿真,同時也支持IEEE常見的各種硬件描述語言標準。

無論從友好的使用界面和調試環境來看,還是從仿真速度和仿真效果來看,ModelSim都可以算得上是業界最優秀的HDL語言仿真軟件。它是惟一的單內核支持VHDL和Verilog混合仿真的仿真器,是做FPG

- 關鍵字:

FPGA ModelSim

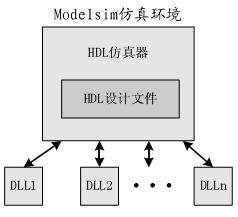

- 1、Modelsim 及 FLI接口介紹

Modelsim是 Model Technology(Mentor Graphics的子公司)的 HDL 硬件描述語言仿真軟件,可以實現 VHDL, Verilog,以及 VHDL-Verilog 混合設計的仿真。除此之外,Modelsim還能夠與 C 語言一起實現對 HDL 設計文件的協同仿真。同時,相對于大多數的 HDL 仿真軟件來說,Modelsim 在仿真速度上也有明顯優勢。這些特點使 Modelsim 越來越受到 EDA設計者、尤其是 FPGA

- 關鍵字:

Modelsim FPGA

- 介紹了以89S52單片機和復雜可編程邏輯器件(CPLD)為核心的數字轉速表的設計。采用CPLD來實現轉速、周期、脈寬和占空比的測量計數,單片機完成測試控制、數據處理和顯示輸出。同時,運用等精度的設計方法,克服了基于傳統測速原理轉速表的測量精度隨被測轉速的下降而降低的缺點。實驗結果表明,所設計的數字轉速表性能穩定,測量精度高。

基于單片機和CPLD的數字轉速表設計

- 關鍵字:

AT89S52 CPLD

- 1 引言

輪式移動機器人是機器人研究領域的一項重要內容.它集機械、電子、檢測技術與智能控制于一體。在各種移動機構中,輪式移動機構最為常見。輪式移動機構之所以得到廣泛的應用。主要是因為容易控制其移動速度和移動方向。因此.有必要研制一套完整的輪式機器人系統。并進行相應的運動規劃和控制算法研究。筆者設計和開發了基于5l型單片機的自動巡線輪式機器人控制系統。

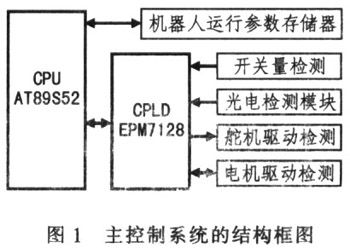

2 控制系統總體設計

機器人控制系統由主控制電路模塊、存儲器模塊、光電檢測模塊、電機及舵機驅動模塊等部分組成,控制系統的框圖如圖1所示

- 關鍵字:

AT89S52 CPLD

- 信號發生器是一種能提供各種頻率、波形和輸出電平電信號的設備。在測量各種電信系統或電信設備的振幅特性、頻率特性、傳輸特性及其它電參數時,以及測量元器件的特性與參數時,用作測試的信號源或激勵源。

無線電導航數字信號源的系統設計,完整參考方案

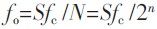

本無線電導航數字信號源總體設計思想采用直接數字頻率合成器(DDS)技術,設計精確的時鐘參考源精度、頻率和相位累加器字長和正弦波函數表,實現研制技術要求的輸出頻率變化范圍、頻率變化步長和頻率精度的調制正弦信號形式。

基于DDFS的程控音頻儀器測試信號源

- 關鍵字:

無線電 FPGA

- 引言

近年來電子信息技術飛速發展,使得各領域對信號源的要求不斷提高,不但要求其頻率穩定度和準確度高,頻率改變方便,而且還要求可以產生任意波形,輸出不同幅度的信號等。DDFS技術是自上世紀70年代出現的一種新型的直接頻率合成技術。DDFS技術是在信號的采樣定理的基礎上提出來的,從“相位”的概念出發,進行頻率合成,不但可利用晶體振蕩的高頻率穩定度、高準確度,且頻率改變方便,轉換速度快,便于產生任意波形等,因此,DDFS技術是目前高精密度信號源的核心技術。

1 DDFS技

- 關鍵字:

FPGA DDFS

- 0 引言

跳頻通信具有較強的抗干擾、抗多徑衰落、抗截獲等能力,已廣泛應用于軍事、交通、商業等各個領域。頻率合成器是跳頻系統的心臟,直接影響到跳頻信號的穩定性和產生頻率的準確度。目前頻率合成主要有三種方法:直接模擬合成法、鎖相環合成法和直接數字合成法(DDS)。直接模擬合成法利用倍頻(乘法)、分頻(除法)、混頻(加法與減法)及濾波,從單一或幾個參考頻率中產生多個所需的頻率。該方法頻率轉換時間快(小于100ns),但是體積大、功耗高,目前已基本不用。鎖相環合成法通過鎖相環完成頻率的加、減、乘、除運算

- 關鍵字:

DDS FPGA

-

測試平臺設計

本實驗主要對數碼管驅動引腳的狀態與預期進行比較和分析,通過仿真,驗證設計的正確性和合理性。數碼管驅動模塊的testbench如下所示:

`timescale 1ns/1ns

module DIG_LED_DRIVE_tb;

reg [23:0]data;

reg clk;

reg rst_n;

wire [7:0]seg;

wire [2:0]sel;

DIG_LED_DRIVE DIG_LED_DRIVE

- 關鍵字:

FPGA 動態掃描

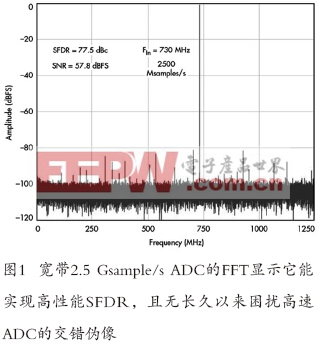

- 隨著模數轉換器(ADC)的設計與架構繼續采用尺寸更小的過程節點,一種新的千兆赫ADC產品應運而生。能以千兆赫速率或更高速率進行直接RF采樣且不產生交織偽像的ADC為通信系統、儀器儀表和雷達應用的直接RF數字化帶來了全新的系統解決方案。

最先進的寬帶ADC技術可以實現直接RF采樣。就在不久前,唯一可運行在GSPS (Gsample/s)下的單芯片ADC架構是分辨率為6位或8位的Flash轉換器。這些器件能耗極高,且通常無法提供超過7位的有效位數(ENOB),這是由于Flash架構的幾何尺寸與功耗限

- 關鍵字:

ADC RF 轉換器 LVDS FPGA

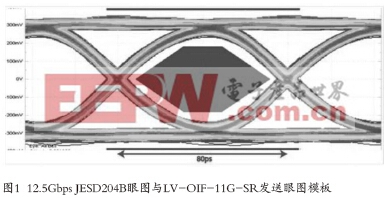

- 1 為不同應用提供不同選擇

對于數據轉換器的高速串行傳輸,不同的應用有不同的選擇。十多年來,數據轉換器制造商一直選擇LVDS作為主要差分信號技術。盡管有些LVDS應用可使用更高的數據速率,但目前該市場上的轉換器廠商可提供的最大LVDS數據速率仍然為0.8至1 Gbps。LVDS技術一直難以滿足轉換器的帶寬要求。LVDS受TIA/EIA 644A規范控制,這是一項LVDS核心制造商的行業標準。該規范可作為設計人員的最佳實踐指南,提高不同廠商的LVDS發送器及接收器兼容性。同樣,沒有完全遵守LVDS

- 關鍵字:

JESD204B LVDS 轉換器 FPGA PHY

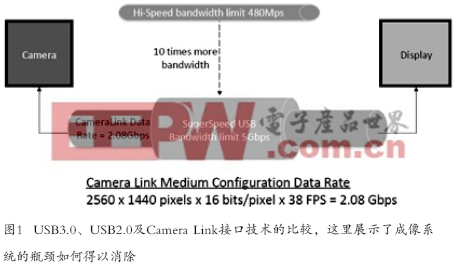

- 高清圖像質量已經快速成為現代家庭中多媒體產品的標準配置。在該領域之外的許多應用中,更高的分辨率、更好的對比度、更大的色深和更快的幀率也都越來越受歡迎,這些應用包括安保、醫療成像和工廠生產線檢測系統等等。當然,盡管增強型成像技術在不久的將來更加流行似乎是板上釘釘的事情,但這將取決于支持更高數據傳輸能力的先進半導體技術的發展。本文將以實例闡述半導體技術所取得的進展。

雖然USB連接標準開始并沒有引起太多關注,但從上世紀90年代中期第一次脫穎而出已經改變了很多,它現在已經遠遠不只是為低數據速率的鼠標和

- 關鍵字:

USB FIFO 緩沖器 FPGA 顯示器

- 領先的技術分銷商駿龍科技有限公司發布了基于Altera MAX® 10的“Mpression Odyssey(奧德賽)”物聯網開發套件和電機驅動方案。Altera的MAX® 10 FPGA在低成本、單芯片、瞬時上電的可編程邏輯器件中提供了先進的處理能力,駿龍科技推出的產品進一步驗證了MAX® 10 FPGA的卓越性能,并進一步豐富了Altera公司的工業解決方案。

“Mpression Odyssey(奧德賽)”開發套件是一

- 關鍵字:

駿龍科技 物聯網 FPGA

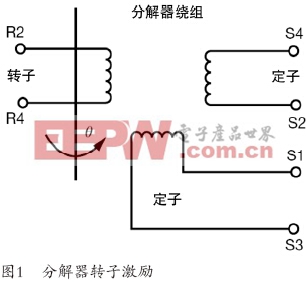

- 1 編碼器和分解器的類型

編碼器分為增量和絕對兩個基本類別。增量編碼器可以監控輪軸上的兩個位置,可以在輪軸每次經過這兩個位置時產生A或B脈沖。獨立的外部電動計數器然后從這些脈沖解讀出轉速和旋轉方向。雖然適用于眾多應用,但是增量式計數器確實存在某些不足。例如,在輪軸停轉情況下,增量編碼器在開始運行之前必須首先通過調回到某個指定校準點來實現自身校準。另外,增量式計數器易受到電氣干擾的影響,導致發送到系統的脈沖不準確,進而造成旋轉計數錯誤。不僅如此,許多增量編碼器屬于光電器件,如果對目標應用有影響,則

- 關鍵字:

編碼器 分解器 RDC FPGA 脈沖

cpld/fpga介紹

您好,目前還沒有人創建詞條cpld/fpga!

歡迎您創建該詞條,闡述對cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473