cpld/fpga 文章 最新資訊

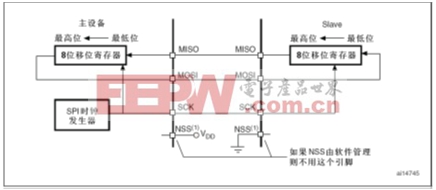

STM32再學習之工程師眼中的SPI

- 前些天,有位網(wǎng)友談到通過FPGA來實現(xiàn)SPI通訊。通過帖子的回復發(fā)現(xiàn)好多網(wǎng)友對SPI通訊還有些疑惑,于是今天就帶著大家從SPI的標準協(xié)議,SPI在STM32單片機上的配置及在74HC595邏輯芯片通訊的實例來全方面認識一下這個既復雜又簡單的通訊協(xié)議。 SPI 是Serial Peripheral Interface的縮寫,直譯為串行外圍設備接口,SPI是Motorola公司推出的一種同步串行通訊方式,是一種四線同步總線,因其硬件功能很強,與SPI有關(guān)的軟件就相當簡單,使MCU有更多的時間處理其他事務

- 關(guān)鍵字: FPGA SPI MCU

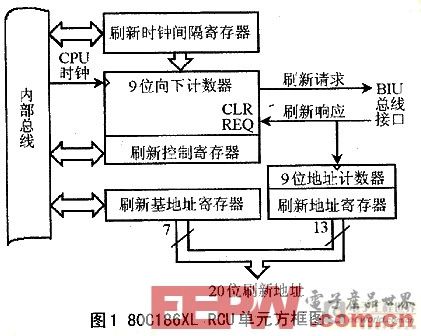

基于CPLD的DRAM控制器設計方法

- 80C186XL16位嵌入式微處理器是Intel公司在嵌入式微處理器市場的上導產(chǎn)品之一,已廣泛應用于電腦終端、程控交換和工控等領(lǐng)域。在該嵌入式微處理器片內(nèi),集成有DRAM RCU單元,即DRAM刷新控制單元。RCU單元可以自動產(chǎn)生DRAM刷新總線周期,它工作于微處理器的增益模式下。經(jīng)適當編程后,RCU將向?qū)⑻幚砥鞯?BIU(總線接口)單元產(chǎn)生存儲器讀請求。對微處理器的存儲器范圍編程后,BIU單元執(zhí)行刷新周期時,被編程的存儲器范圍片選有效。 存儲器是嵌入式計算機系統(tǒng)的重要組成部分之一。通常采用靜態(tài)

- 關(guān)鍵字: CPLD DRAM VHDL

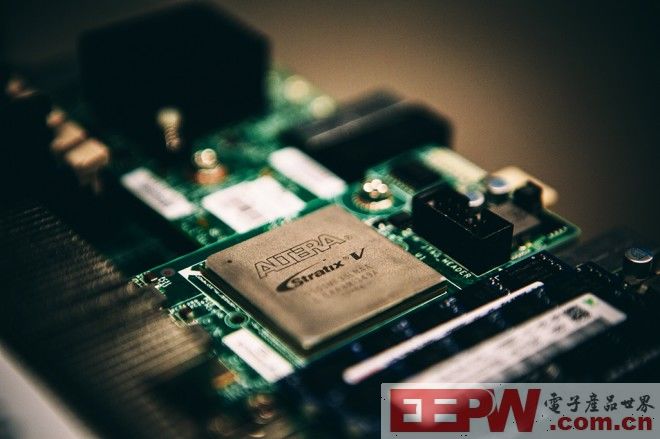

Altera可編程邏輯成為軟件定義數(shù)據(jù)中心的關(guān)鍵DNA

- Altera公司(NASDAQ: ALTR)今天宣布,其FPGA成為軟件定義數(shù)據(jù)中心(SSDC)開發(fā)的核心組成,Altera與微軟研究院以及必應合作,加速網(wǎng)絡搜索引擎部分的開發(fā)。Altera的現(xiàn)場可編程邏輯陣列(FPGA)加速了大量數(shù)據(jù)在服務器上的處理過程,幫助解決大數(shù)據(jù)難題,滿足了巨大的分布式工作負載需求。 微軟在名為《一種加速大規(guī)模數(shù)據(jù)中心服務的重新配置架構(gòu)》的研究論文中共享了關(guān)鍵開發(fā)內(nèi)容,在明尼阿波利斯舉行的41屆計算機體系結(jié)構(gòu)國際大會 (ISCA)上宣讀此篇論文。這篇論文詳細介紹了怎樣應

- 關(guān)鍵字: Altera FPGA 可編程邏輯

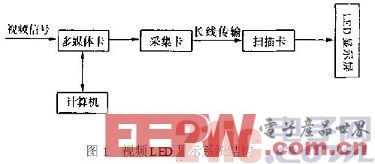

基于CPLD的LED顯示屏控制電路設計

- 引言 近年來,隨著計算機技術(shù)和集成電路技術(shù)的飛速發(fā)展,得到廣泛應用的大屏幕顯示系統(tǒng)當屬視頻LED顯示系統(tǒng)。在LED顯示技術(shù)中,由于紅色、綠色發(fā)光二極管的亮度、光效色差等性能也得到了很大的提高,加之計算機多媒體制作軟件的發(fā)展,現(xiàn)在偽彩視頻LED顯示系統(tǒng)的制造成本大大降低,應用領(lǐng)域不斷增加。這種偽彩色視頻LED顯示系統(tǒng)采用了計算機多媒體技術(shù),全同步動態(tài)顯示視頻圖像,圖像清晰,亮度高,無拼縫,每種顏色的視頻灰度等級已經(jīng)由早期的16級灰度上升現(xiàn)在的256灰度,隨著大規(guī)模集成電路和專用元器件的發(fā)展,256

- 關(guān)鍵字: CPLD LED 顯示屏

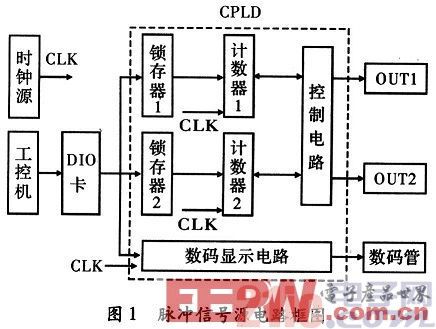

一種基于CPLD的單片機脈沖信號源設計

- 單片機產(chǎn)生的脈沖信號源由于是靠軟件實現(xiàn)的,所以輸出頻率及步進受單片機時鐘頻率、指令數(shù)和指令執(zhí)行周期的限制。文中介紹了一種以CPLD為核心的脈沖信號源,脈沖信號源的參數(shù)(頻率、占空比)由工控機通過I/O板卡設置,設定的參數(shù)由數(shù)碼管顯示,這種脈沖信號源與其它脈沖信號發(fā)生電路相比具有輸出頻率高、步進小(通過選用高速CPLD可提高頻率及縮小步進)、精度高、參數(shù)調(diào)節(jié)方便、易于修改等優(yōu)點。 1系統(tǒng)組成及工作原理 脈沖信號源電路核心采用一片可編程邏輯器件EPM7128SLC84—10,它屬于

- 關(guān)鍵字: CPLD Altera MAX7000

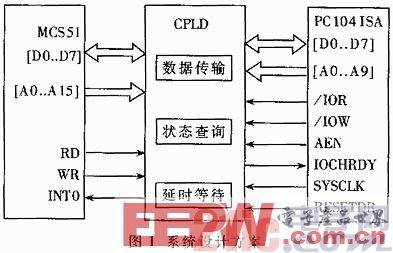

基于CPLD的單片機與ISA總線接口的并行通信設計

- 摘要:介紹了用ALTERA公司MAX7000系列CPLD芯片實現(xiàn)單片機與PC104ISA總線接口之間的關(guān)行通信。給出了系統(tǒng)設計方法及程序源代碼。 關(guān)鍵詞:CPLD ISA總線 并行通信 CPLD(Complex Programmable Logic Device)是一種復雜的用戶可編程邏輯器件,由于采用連續(xù)連接結(jié)構(gòu),易于預測延時,從而使電路仿真更加準確。CPLD是標準的大規(guī)模集成電路產(chǎn)品,可用于各種數(shù)字邏輯系統(tǒng)的設計。近年來,由于采用先進的集成工藝和大指量生產(chǎn),CPLD器件成本不斷下降,集

- 關(guān)鍵字: CPLD ISA總線 并行通信

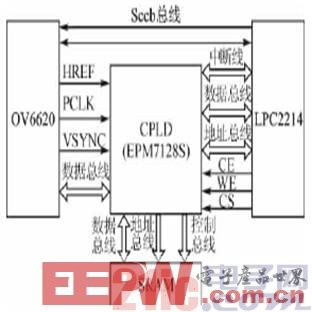

一種基于ARM和CPLD的嵌入式視覺系統(tǒng)設計

- 目前,關(guān)于視覺系統(tǒng)的研究已經(jīng)成為熱點,也有開發(fā)出的系統(tǒng)可供參考。但這些系統(tǒng)大多是基于PC機的,由于算法和硬件結(jié)構(gòu)的復雜性而使其在小型嵌入式系統(tǒng)中的應用受到了限制。上述系統(tǒng)將圖像數(shù)據(jù)采集后,視覺處理算法是在PC機上實現(xiàn)的。隨著嵌入式微處理器技術(shù)的進步,32位 ARM處理器系統(tǒng)擁有很高的運算速度和很強的信號處理能力,可以作為視覺系統(tǒng)的處理器,代替PC機來實現(xiàn)簡單的視覺處理算法。下面介紹一種基于ARM和 CPLD的嵌入式視覺系統(tǒng),希望能分享嵌入式視覺開發(fā)過程中的一些經(jīng)驗。 1 系統(tǒng)方案與原理 在嵌入式視覺的

- 關(guān)鍵字: ARM CPLD

硅谷采風

- 4月初,筆者作為亞歐記者團的成員,訪問了美國硅谷,以下是部分公司的趨勢。 Lattice CEO: 新型FPGA是高增長的主要驅(qū)動力 定位于低成本、低功耗和小尺寸FPGA領(lǐng)導者的Lattice,2013財年營收達3.3億美元,比2012年上升19%,其中以智能手機為代表的消費類產(chǎn)品線成長了180%,增速驚人。總裁兼CEO Darin Billerbeck說,公司主要驅(qū)動力是在新產(chǎn)品上,2013財年新產(chǎn)品占了該公司營收的45 %,而主流產(chǎn)品約44%,成熟產(chǎn)品只有10%左右。 Latti

- 關(guān)鍵字: FPGA IC GEO 201406

廠商聯(lián)合應對日益復雜的SDR設計

- 繼去年“2013年ADI設計峰會”第一次共同舉行新聞發(fā)布會以后,這是ADI公司與Xilinx第二次坐在一起面對媒體,此次共同發(fā)布的內(nèi)容是面向電子設計工程師推介高效的系統(tǒng)級SDR(軟件定義無線電)解決方案。 說實話,大家可能更關(guān)心這兩家巨頭公司為何會頻頻攜手合作呢? 應對SDR設計工程師面臨全新設計挑戰(zhàn) 從快速發(fā)展的通訊市場來看,電子設備開發(fā)工程師面臨著日益嚴峻的挑戰(zhàn)。 首先是市場挑戰(zhàn)。第一個是產(chǎn)品上市時間的壓力,誰首先占領(lǐng)這個市場,誰就占領(lǐng)了先機;第二個

- 關(guān)鍵字: ADI Xilinx FPGA 201406

物聯(lián)網(wǎng)時代本土芯片企業(yè)如何定位?

- 自從2000年18號文件”頒布以來,中國已經(jīng)擁有過超600余家的本土芯片設計企業(yè),就在大家還在為“CPU,F(xiàn)PGA,DSP,Memory”這四大通用半導體器件而努力時,忽然來到了“物聯(lián)網(wǎng)時代”,面對“低功耗、高性能、小型化、低成本”這4個并存的嚴苛條件,中國本土芯片企業(yè)該如何定位才能保證生存并發(fā)展,成了一個非常現(xiàn)實的課題。特別是當客戶需求開始向系統(tǒng)級方向發(fā)展時,中國本土芯片產(chǎn)品如何形成可以滿足需求的系統(tǒng)解決方案,這是一個大大的挑戰(zhàn)。

- 關(guān)鍵字: 物聯(lián)網(wǎng) MCU FPGA 201406

基于FPGA的多路相干DDS信號源設計

- 摘要:傳統(tǒng)的多路同步信號源常采用單片機搭載多片專用DDS芯片配合實現(xiàn)。該技術(shù)實現(xiàn)復雜,且在要求各路同步相干可控時難以實現(xiàn)。本文在介紹了DDS原理的基礎上,給出了用Verilog_HDL語言實現(xiàn)相干多路DDS的工作原理、設計思路、電路結(jié)構(gòu)。利用Modelsim仿真驗證了該設計的正確性,本設計具有調(diào)相方便,相位連續(xù),頻率穩(wěn)定度高等優(yōu)點。 關(guān)鍵詞:DDS;現(xiàn)場可編程門陣列(FPGA);相位累加器;Verilog_HDL 實現(xiàn)信號源的多路同步輸出且各路間擁有固定的相位關(guān)系,在雷達、通信等多領(lǐng)域有著重要的應用。

- 關(guān)鍵字: FPGA DDS

基于DSP+CPLD的嵌入式高速圖像通信系統(tǒng)設計

- 1 引言 隨著現(xiàn)代的圖形采集技術(shù)發(fā)展迅速,各種基于ISA,PCI,USB1.1等總線的圖形采集卡速度已經(jīng)不能滿足用戶的需求,而采用 USB2.0以后就可以解決這個傳輸速度上的瓶頸,USB2.0的速度是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續(xù)處理的要求。系統(tǒng)中采用 DSP+CPLD的硬件設計方案,采用現(xiàn)場可編程芯片 CPLD及兩片 SRAM構(gòu)成的圖像采集和存儲系統(tǒng),可以根據(jù)不同的需要進行現(xiàn)場編程,具有通用性好、價格相對便宜,易于系統(tǒng)調(diào)試,升級等特點。系統(tǒng)中 CPLD選擇的型號是 ALTER

- 關(guān)鍵字: DSP CPLD

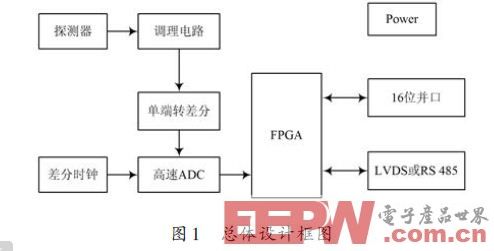

一種基于FPGA的數(shù)字核脈沖分析器設計

- 0 引言 多道脈沖幅度分析儀和射線能譜儀是核監(jiān)測與和技術(shù)應用中常用的儀器。20世紀90年代國外就已經(jīng)推出了基于高速核脈沖波形采樣和數(shù)字濾波成型技術(shù)的新型多道能譜儀,使數(shù)字化成為脈沖能譜儀發(fā)展的重要方向。國內(nèi)譜儀技術(shù)多年來一直停留在模擬技術(shù)水平上,數(shù)字化能譜測量技術(shù)仍處于方法研究階段。為了滿足不斷增長的高性能能譜儀需求,迫切需要研制一種數(shù)字化γ能譜儀。通過核脈沖分析儀顯示在顯示器上的核能譜幫助人們了解核物質(zhì)的放射性的程度。 1 數(shù)字多道分析儀的優(yōu)勢 國內(nèi)很大一部分學者采用核譜儀模擬電路的方

- 關(guān)鍵字: FPGA AD9649

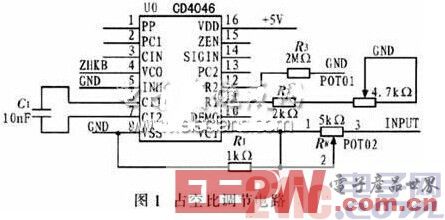

基于CPLD的臭氧電源控制系統(tǒng)設計

- 臭氧被喻為“綠色”消毒產(chǎn)品,在國內(nèi)外得到廣泛應用。近年來,臭氧技術(shù)作為環(huán)保產(chǎn)業(yè)的重要組成部分,受到越來越多人的重視。相關(guān)產(chǎn)品已從飲用水處理系統(tǒng)拓展到污水處理、空氣凈化、家庭環(huán)境污染防治、醫(yī)療保健等領(lǐng)域。 臭氧發(fā)生器供電電源是臭氧發(fā)生器的重要組成部分,供電電源的電壓、頻率和波形是影響臭氧發(fā)生器效率的重要因素。發(fā)生器的結(jié)構(gòu)、氣源和冷卻系統(tǒng)確定后,電源系統(tǒng)的性能與品質(zhì)就成為影響發(fā)生器效率的關(guān)鍵。上世紀80年代后,半導體器件的發(fā)展使臭氧電源發(fā)生質(zhì)的變化,逆變式電源成為臭氧發(fā)生電源的主要形

- 關(guān)鍵字: CPLD VCO

cpld/fpga介紹

您好,目前還沒有人創(chuàng)建詞條cpld/fpga!

歡迎您創(chuàng)建該詞條,闡述對cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司