- PLL鎖相環的特性、應用與其基本工作過程-PLL(Phase Locked Loop),也稱為鎖相環路(PLL)或鎖相環,它能使受控振蕩器的頻率和相位均與輸入參考信號保持同步,稱為相位鎖定,簡稱鎖相。

- 關鍵字:

pll 鎖相環

- PLL鎖相環的基本結構及工作原理-PLL(Phase Locked Loop): 為鎖相回路或鎖相環,用來統一整合時脈訊號,使高頻器件正常工作,如內存的存取資料等。PLL用于振蕩器中的反饋技術。 許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步。

- 關鍵字:

pll 鎖相環

- 時鐘設備設計使用 I2C 可編程小數鎖相環 (PLL),可滿足高性能時序需求,這樣可以產生零 PPM(百萬分之一)合成誤差的頻率。高性能時鐘 IC 具有多個時鐘輸出,用于驅動打印機、掃描儀和路由器等應用系統的子系統,例如處理器、FPGA、數據轉換器等。此類復雜系統需要動態更新參考時鐘的頻率,以實現 PCIe 和以太網等其它諸多協議。 時鐘 IC 屬于 I2C 從器件,需要主控制器來

- 關鍵字:

I2C PLL

- 基于單片機和CPLD的DDS正交信號源,其頻率幅度可精密控制,擴展輸出頻率達300 kHz,增加掃頻輸出功能。采用紅外鍵盤控制頻率和幅度,采用液晶同步顯示信號的頻率和幅度;輸出端產生正弦波、方波、三角波、鋸齒波,梯形波、短形波、頻率突變的方波、尖脈沖數字信號等,且具有掃頻輸出的功能。測試結果表明,系統穩定可靠,人機交互界面友好,操作簡單方便。

- 關鍵字:

DDS 正交信號源 CPLD 濾波器 DT9205 AT28C64

- 本系統在分析數字調制技術和DDS原理的基礎上,詳述了一種基于FPGA的DSP技術和DDS技術的適合于軟件無線電使用的可控數字調制器的設計過程,并在系統中進行了功能驗證。此調制器以FPGA硬件平臺為核心,可實現ASK,FSK,PSK,QAM等調制方式,靈活性強。

- 關鍵字:

數字調制技術 軟件無線電 DDS

- 介紹了一種基于DSP+FPGA芯片技術的高精度程控交流電源的實現方法,利用FPGA實現了任意波形發生功能,并對功率逆變等電路進行了詳細的分析和設計,最后給出了實驗結果以及相關波形。

- 關鍵字:

任意波形發生 諧波 DDS

- 在應用FPGA進行DDS系統設計過程中,選擇芯片的運行速度優化和資源利用優化常常是相互矛盾的,從發展趨勢和運算要求看,系統速度指標的意義比面積指標更趨重要。基于此,介紹了一種流水線結構來優化傳統的相位累加器,在QuartusⅡ開發環境下搭建系統模型、仿真及下載,并采用嵌入式邏輯分析儀分析和驗證了實驗結果。該系統可以完成多位頻率控制字的累加,能夠產生正弦波、方波和三角波,具有良好的實時性。

- 關鍵字:

流水線相位累加器 DDS FPGA

- 本文論述了利用用FPGA來開發DDS函數發生器的總體設計思路,詳細討論了任意波形產生、頻率精確調整、雙路移相輸出、PWM調制波產生、D/A轉換與濾波電路、鍵盤與顯示等諸方面軟硬件實現方法。 整個設計

- 關鍵字:

DDS 任意波形發生器 FPGA

- 本文以Hynix公司生產的HMS30C7202工業級處理器作為控制器,以矩陣鍵盤作為輸入設備,以AMPIRE公司生產的AM-320240LTNQW-00H TFT LCD顯示屏作為顯示輸出設備,研究設計了相應的硬件電路與顯示驅動程序,在此基礎上完成了人機交互中英文顯示系統的設計。

- 關鍵字:

信號源 DDS LCD顯示屏

- 現代直接數字頻率合成器(DDS)通常利用累加器和數字頻率調諧字(FTW)在累加器輸出端產生周期性的N位數字斜坡(見圖1)。 此數字斜坡可依據公式1定義DDS的輸出頻率(fO),其中fS為DDS采樣速率(或系統時鐘頻率)。

- 關鍵字:

直接數字頻率合成器 DDS FTW

- 最初,對于DUT的幅頻特性的測試是在固定頻率點上逐點進行。這種測試方法繁瑣、費時,且不直觀,有時還會得出片面的結果。例如,測量點之間的諧振現象和網絡特性的突變點常常被漏掉。

- 關鍵字:

DDS 幅頻特性

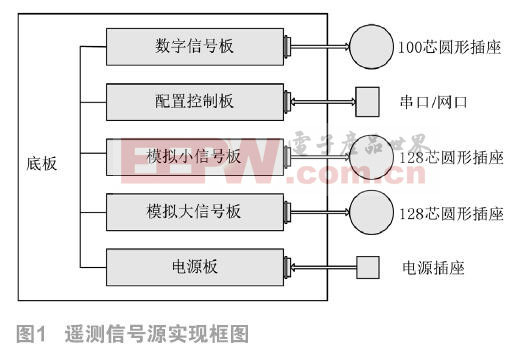

- 遙測信號模擬源是多通道信號發生器,模擬彈載組件,輸出模擬及數字信號供遙測艙采集,以判斷遙測艙是否正常。本設計基于DDS及數字可編程技術,采用DAC芯片AD5312、運放,RS422、429、LVDS等接口芯片,編寫FPGA模塊,最終實現多達100路模擬電壓及40路數字信號輸出,并可在計算機上通過網絡進行參數配置。該信號源輸出信號種類多,參數配置靈活方便,可滿足多個遙測組件的測試需求。

- 關鍵字:

遙測 信號源 DDS AD5312 測試 201706

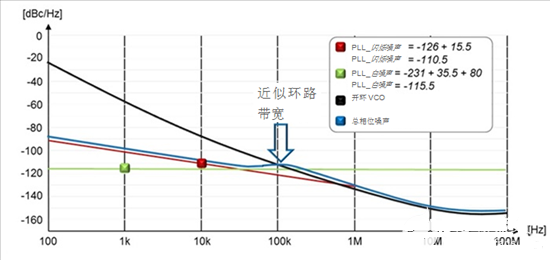

- 也許你也會跟我一樣認為典型數據表中的某些規格難以理解,這是因為其中涵蓋了一些你不太熟悉的隱含慣例。對許多RF系統工程師而言,其中一種規格便是鎖相環(PLL)中的相位噪聲。當信號源被用作本機振蕩器(LO)或高速時鐘時,相位噪聲性能對滿足系統要求起到了重要作用。最初從數據表中推斷出該規格時似乎就像一個獨立的項目。下面我來講解一下如何通過讀取PLL的相位噪聲規格來對您的無線電或高速應用可達到的性能進行初步評估。 注意,PLL是一種控制回路,這種系統具備頻率響應功能。參考路徑中生成的噪聲受控于回路中對系統輸

- 關鍵字:

PLL VCO

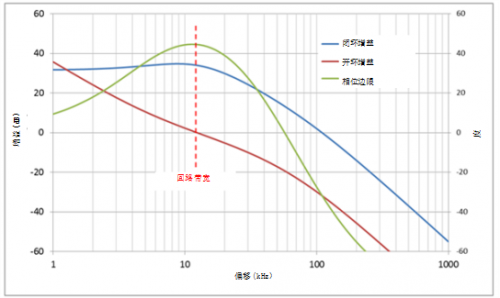

- 假設您已經通過迭代信息傳遞相位邊限和回路帶寬在鎖相環(PLL)上花費了一些時間。但遺憾地是,還是無法在相位噪聲、雜散和鎖定時間之間達成良好的平衡。感到泄氣?想要放棄?等一下!你是否試過伽馬優化參數? 伽馬優化參數 伽馬是一個數值大于零的變量。當伽馬等于1時,相位邊限在回路頻處會達到最大值(圖1)。很多回路濾波器設計方法把伽馬值設為1,這是個很好的起點,但還有進一步優化的空間。 圖1:伽馬等于1時的波德圖 伽馬能夠有效用于優化帶內相位噪聲,尤其是因壓控振蕩器 (VCO) 帶來

- 關鍵字:

PLL 回路濾波器

dds+pll介紹

您好,目前還沒有人創建詞條dds+pll!

歡迎您創建該詞條,闡述對dds+pll的理解,并與今后在此搜索dds+pll的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473