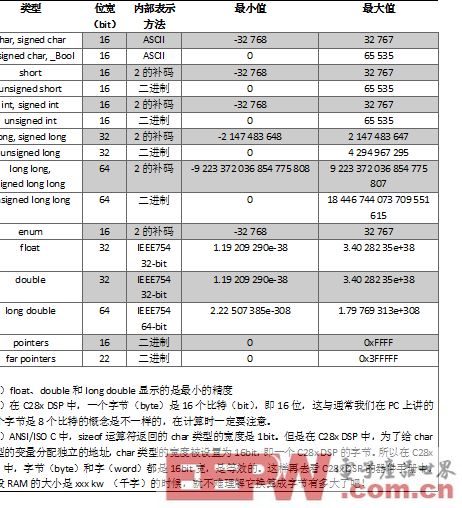

DSP的C/C++編程時有多少種數據類型?float,double和long double,long和long long這些繞口的名字究竟有什么區別?數據類型使用不正確又會有什么后果?如果你感覺說不清楚,那我們來看看這些到底都是何方神圣吧:

表1 C28x C/C++支持的數據類型

Ø 64位整數的處理

從上面的表中,可以看出

關鍵字:

DSP 數據類型 C/C++

前面我們提到了使用編譯器的優化選項進行不同級別的代碼優化的方法(請參考http://cqxgywz.com/article/203169.htm)。俗話說“好馬配好鞍”,即使我們有了強大的代碼優化工具,使得我們書寫的符合ANSI/ISO C/C++的代碼能被高效執行,我們在寫代碼時也要考慮到一些必要的原則,從而既能實現代碼的優化,也能保證代碼的安全,使得優化操作不會讓我們的代碼產生預期之外的結果。下面我們就來看一下在使用代碼優化時,必須考慮的五大問題。

1. 小心

關鍵字:

DSP 代碼優化 C/C++

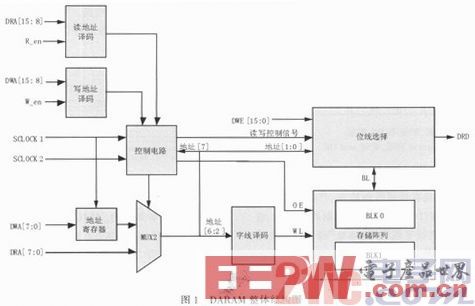

摘要:介紹了一種DSP芯片內嵌DARAM的電路結構,詳細分析了接口電路中各個模塊的功能,包括地址譯碼電路,字線譯碼電路,位線選擇電路及控制電路四部分內容。著重介紹了控制電路的原理,及如何實現一個周期“雙存取”的功能。利用數模混合仿真工具ADvance MS對整體電路進行仿真,結果證明DARAM可以在一個時鐘周期內完成一次讀和一次寫操作,實現預期的功能,為DSP設計乃至SOC的設計工作提供了參考。

在復雜的系統級微處理器設計中,存儲器負責系統程序和數據的儲存,是整個系統的重

關鍵字:

DSP DARAM ADvance

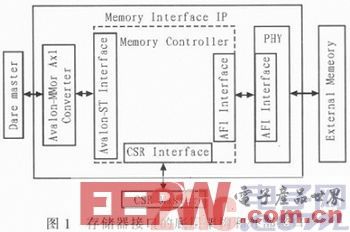

摘要:文中詳細地分析了Altera公司Cyclone V FPGA器件的硬核存儲控制器底層架構和外部接口,并在此基礎上對Controller和PHY進行了功能仿真。仿真結果表明硬核存儲控制器和PHY配合工作時的功能與設計預期相符,性能優良,適合于在當前FPGA的外部存儲帶寬需求日益增長的場合下應用。

如今,越來越多的應用場景都需要FPGA能夠和外部存儲器之間建立數據傳輸通道,如視頻、圖像處理等領域,并且對數據傳輸通道的帶寬也提出了較大的需求,這就導致了FPGA和外部Memory接口的實際有效帶寬

關鍵字:

FPGA Altera Cyclone V

萊迪思半導體公司超低功耗、小尺寸、客制化解決方案的FPGA市場領導者,今日宣布推出iCE40 Ultra™產品系列,獨家集成了紅外遙控、條形碼、觸控、用戶識別、計步器等新興功能以及可供定制的極大靈活性,使消費類移動電子設備制造商能夠快速實現體現產品差異化的“殺手級”功能。

相比競爭對手的解決方案,iCE40 Ultra FPGA在提供5倍更多功能的同時減小了30%的尺寸。并且相比以前的器件,功耗降低高達75%。上述優勢為開發者們實現了更緊湊的設計布局和更長的電

關鍵字:

萊迪思 FPGA iCE40 Ultra

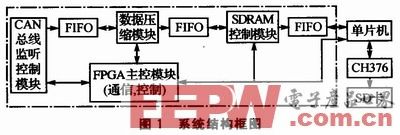

引言

CAN(Controller Area Network,控制器局域網)總線是德國Bosch公司在20世紀80年代初,為了解決現代汽車中眾多的控制與測試儀器之間的數據交換而開發的一種串行數據通信協議。它的短幀數據結構、非破壞性總線性仲裁技術以及靈活的通信方式適應了汽車的實時性和可靠性要求,倍受汽車生產廠商的青睞。隨著汽車電子技術的發展,汽車上的ECU(Electronic Control Unit,電子控制單元)越來越多,如電控燃油噴射系統、防抱死制動系統、防滑控制系統等,相應的數據量也越來

關鍵字:

CAN總線 FPGA MSP430

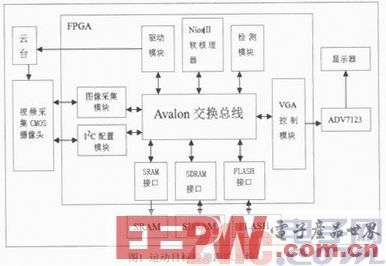

摘要:文章是以Nios II處理器為中心的視頻運動目標檢測跟蹤系統,通過CMOS圖像傳感器采集視頻圖像信息,采用幀間差分法檢測運動目標,形心跟蹤算法對目標進行跟蹤,最后在VGA顯示器上顯示視頻中運動物體。實驗結果表明,該系統可達到運動目標檢測跟蹤的理想結果。

0 引言

運動目標檢測跟蹤就是將運動的目標從視頻圖像序列中檢測出來,對其進行跟蹤。在計算機視覺領域和智能視頻監控系統中,目標檢測與跟蹤系統是一個最要的研究內容,該系統在很多領域中經得到廣泛的應用,例如在家庭住宅小區、智能交通、銀行、超

關鍵字:

FPGA Nios II 圖像傳感器

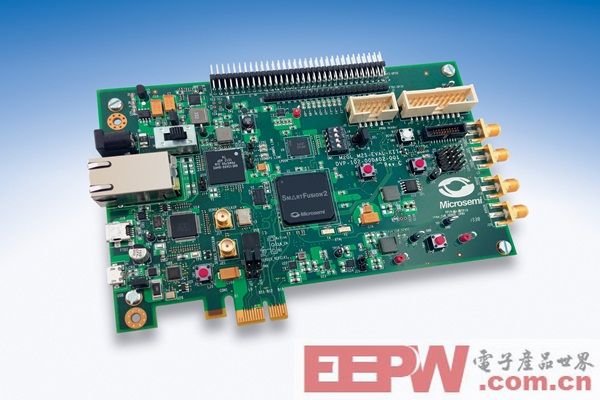

致力于提供功耗、安全、可靠與高性能半導體技術方案的領先供應商美高森美公司發布了新一代先進的SmartFusion®2 SoC FPGA評測工具套件。新一代SmartFusion2評測工具套件是一款定位于易于使用、功能豐富、價格相宜的平臺,可讓設計人員快速、容易地加速其應用的評測或樣品構建。使用美高森美的主流SmartFusion2 FPGA器件,OEM廠商可以充分利用這些器件在同級中最低功耗、高可靠性性能和同級最佳安全性技術,來構建高度差異化產品,并幫助他們贏得顯著的上市時間優勢。

一個

關鍵字:

美高森美 SmartFusion2 FPGA

FPGA可以存在于任何系統應用中

問:Altera產品的應用領域有哪些?

答:我們的FPGA可應用于任何領域,從有線通信&無線通信,到工業、汽車、國防&汽車,還有計算、存儲%網絡領域等,為客戶提供系統級的解決方案。

???????因為Altera提供的是可編程邏輯,所以更多的是提供通用芯片,而且在上面承載了軟件和一些應用,是平臺式的解決方案,是客戶的系統級合作伙伴。

問:高端產品占Alte

關鍵字:

FPGA Altera 可編程邏輯

TVS,領先的軟件測試和硬件驗證服務提供商近期宣布,將繼續其全球業務擴張的步伐。TVS與TopBrain Design Systems已正式簽署合作協議,TVS將通過在中國的合作伙伴TopBrain擴展其在中國的產品與服務。TopBrain Design Systems是一家成立于中國境內、為復雜電子產品設計的組織提供先進驗證解決方案的高科技公司。

TVS最近在南韓和新加坡都贏得了客戶,在上述兩個地區TVS都開設了分支機構,因此與TopBrain合作將更好的拓展TVS在亞洲的業務。

Rog

關鍵字:

TVS SOC FPGA

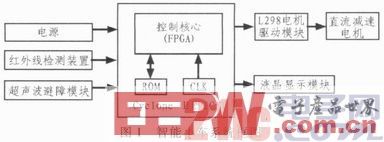

摘要:文中介紹了一種基于FPGA的智能小車設計方案,系統采用FPGA產生的PWM波調控小車速度,紅外線傳感器TCRT5000檢測路面上的黑色軌跡,井將檢測到的信號反饋給控制芯片FPCA,FPCA由采集到的信號發出指令,控制小車電機驅動電路以調整行駛方向,從而使小車能夠沿著黑色軌跡自動行駛,同時利用了超聲波模塊實時的檢測前邊的障礙物,實現了小車的避障循跡功能。

隨著FPGA從可編程邏輯芯片升級為可編程系統級芯片,其在電路中的角色已經從最初的邏輯膠合延伸到數字信號處理、接口、高密度運算等廣闊的范圍,

關鍵字:

FPGA 智能小車 CycloneⅡEP2 C5T

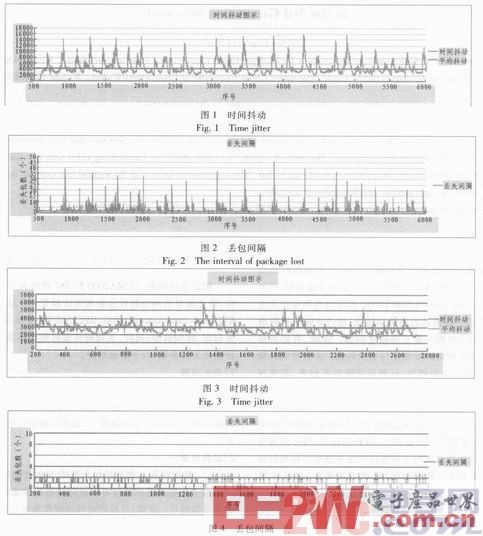

摘要:為了實現基于TMS320DM365編碼的實時視頻流通過CDMA2000 EVDO網絡傳輸后能夠流暢播放的功能,同時緩解視頻傳輸延遲和馬賽克現象,文中通過對CDMA2000 EVDO網絡傳輸過程中數據丟包率和時間抖動等參數的分析和論證,提出了在視頻編碼發送端進行速率整形以適應網絡帶寬的方法。該方法主要是在視頻數據編碼完成后,通過CDMA2000 EVDO網絡發送時,對發送數據的速率做出了兩次平滑調整。其結果表明,該方法能有效的改善傳輸視頻的質量,提升視頻的流暢性。

現有CDMA2000 EV

關鍵字:

DSP CDMA 2000 無線傳輸

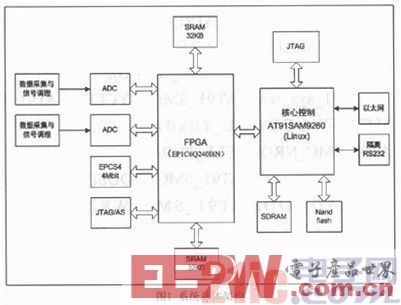

摘要:文章以嵌入式和數據采集技術為基礎,研究設計并實現了基于ARM+FPGA體系架構面向高速實時數據采集應用的一種實用新型智能控制器。本文闡述了主處理器ARM最小系統、協處理器FPGA最小系統和ARM與FPGA通信接口等硬件系統技術的實現,以及Linux FPGA字符設備驅動程序開發、協處理器FPGA控制程序和主處理器ARM應用程序設計。智能控制器運用FPGA并行運算處理結構的優勢,控制ADC進行高速數據采集。FPGA還可配置成軟核處理器-Nios II嵌入式處理器,與ARM構成雙核處理器系統。智能控

關鍵字:

ARM FPGA 數據采集

電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

關鍵字:

FPGA GPU DAC驅動 AESA

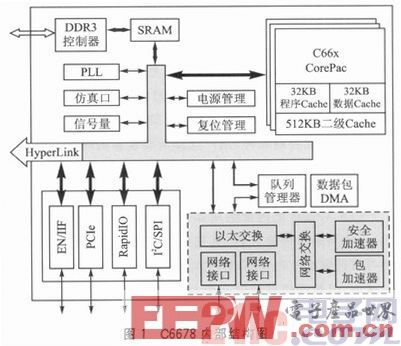

摘要:多核數字信號處理器(DSP)具有豐富的外設接口,每個外設接口具有各自獨立的參考時鐘。由于多核DSP具有較快的數據處理能力,對外設接口的時鐘要求較高。當多個接口協同工作時,對時鐘的同步要求較高。本文介紹了多核數字信號處理器丁MS320C6678的時鐘設計,通過時鐘芯片CDCM6208提供多路不同工作頻率的時鐘信號到DSP,文中介紹了時鐘芯片的初始化和設置以及詳細的軟硬件設計方法。

引言

多核處理器是最近快速發展的電子器件,單個芯片內集成了多個同構或者異構的處理器,使得其計算處理能力得到

關鍵字:

DSP MS320C6678 同步時鐘

dsp+fpga介紹

您好,目前還沒有人創建詞條dsp+fpga!

歡迎您創建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473