EEPW首頁(yè) >>

主題列表 >>

dsp+fpga

dsp+fpga 文章 最新資訊

基于FPGA的DDS設(shè)計(jì)及實(shí)現(xiàn)

- 針對(duì)DDS頻率轉(zhuǎn)換時(shí)間短,分辨率高等優(yōu)點(diǎn),提出了基于FPGA芯片設(shè)計(jì)DDS系統(tǒng)的方案。該方案利用A1tera公司的QuartusⅡ開(kāi)發(fā)軟件,完成DDS核心部分即相位累加器和ROM查找表的設(shè)計(jì),可得到相位連續(xù)、頻率可變的信號(hào),并通過(guò)單片機(jī)配置FPGA的E2PROM完成對(duì)DDS硬件的下載,最后完成每個(gè)模塊與系統(tǒng)的時(shí)序仿真。經(jīng)過(guò)電路設(shè)計(jì)和模塊仿真,驗(yàn)證了設(shè)計(jì)的正確性。由于FPGA的可編程性,使得修改和優(yōu)化DDS的功能非常快捷。

- 關(guān)鍵字: FPGA DDS

低功耗DSP市場(chǎng)升級(jí)在即,ADI TI相繼發(fā)力

- 對(duì)于任何半導(dǎo)體廠商來(lái)講,低功耗永遠(yuǎn)是其追求的目標(biāo),DSP廠商也是如此。ADI及TI兩大DSP主要供貨商日前先后推出了其最新的低功耗DSP處理器,瞄準(zhǔn)滿足移動(dòng)、工業(yè)等對(duì)于功耗及價(jià)格敏感的應(yīng)用。 ADI公司處理器及DSP技術(shù)部市場(chǎng)總監(jiān)Colin Duggan表示,ADI BF592目標(biāo)市場(chǎng)主要包括,條碼掃描儀、智能計(jì)算、音頻處理、手持式設(shè)備、自動(dòng)外部除顫器及駕駛員輔助系統(tǒng)等,而尤其適用于目前的智能儀表中。 “由于不同國(guó)家有不同的要求,且軟件無(wú)線電標(biāo)準(zhǔn)正在制定之中,因此需要具備足夠的

- 關(guān)鍵字: ADI DSP

Actel FPGA現(xiàn)可配合加密內(nèi)核對(duì)抗DPA攻擊

- 愛(ài)特公司(Actel CorporaTIon) 宣布其多種FPGA產(chǎn)品現(xiàn)可搭配使用加密內(nèi)核,對(duì)抗差分功率分析(differential Power analysis, DPA)攻擊。采用SmartFusion、Fusion、ProASIC3和 IGLOO的設(shè)計(jì)人員現(xiàn)可通過(guò)使用IP Cores公司(IP Cores, Inc.)的AES、GCM或ECC IP內(nèi)核,保護(hù)其密鑰不受DPA攻擊。IP Cores是專(zhuān)業(yè)提供主要用于安全和加密領(lǐng)域的半導(dǎo)體用IP內(nèi)核的供應(yīng)商,而這些內(nèi)核則是首次商業(yè)化地用于FPGA的

- 關(guān)鍵字: Actel FPGA

ADI公司以超低成本、800 MMAC DSP擴(kuò)展Blackfin系列

- ADI),全球領(lǐng)先的高性能信號(hào)處理解決方案供應(yīng)商,最近推出800MMAC/400MHz性能的Blackfin ADSP-BF592,萬(wàn)片訂量售價(jià)僅3美元/片。Blackfin BF592的活動(dòng)功耗低至88 mW,采用小型9 mm x 9 mm 64引腳LFCSP封裝,該產(chǎn)品的問(wèn)世使得許多具有功耗限制的小尺寸應(yīng)用也能集成高性能DSP(數(shù)字信號(hào)處理器),充分滿足工業(yè)、醫(yī)療、視頻、音頻和通用市場(chǎng)的需求。 ADI公司DSP處理器核心技術(shù)部門(mén)業(yè)務(wù)開(kāi)發(fā)經(jīng)理Richard Murphy表示:“低成

- 關(guān)鍵字: ADI Blackfin DSP

基于DSP的機(jī)器人視覺(jué)伺服系統(tǒng)

- 電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術(shù)中心和交流中心,是電子產(chǎn)品的市場(chǎng)中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡(luò)家園

- 關(guān)鍵字: DSP 機(jī)器人 伺服系統(tǒng) 機(jī)器視覺(jué) TMS320C6201 圖像處理

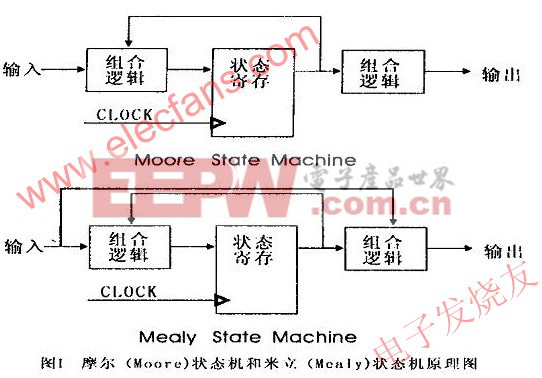

FPGA/CPLD狀態(tài)機(jī)的穩(wěn)定性設(shè)計(jì)

- FPGA/CPLD狀態(tài)機(jī)的穩(wěn)定性設(shè)計(jì), 隨著大規(guī)模和超大規(guī)模FPGA/CPLD器件的誕生和發(fā)展,以HDL(硬件描述語(yǔ)言)為工具、FPGA/CPLD器件為載體的EDA技術(shù)的應(yīng)用越來(lái)越廣泛.從小型電子系統(tǒng)到大規(guī)模SOC(Systemonachip)設(shè)計(jì),已經(jīng)無(wú)處不在.在FPGA/CPLD設(shè)計(jì)中,狀

- 關(guān)鍵字: 設(shè)計(jì) 穩(wěn)定性 狀態(tài) FPGA/CPLD

一種基于PXI的高速數(shù)字化儀模塊的設(shè)計(jì)應(yīng)用

- PXI總線是NI公司在計(jì)算機(jī)外設(shè)總線PCI的基礎(chǔ)上實(shí)現(xiàn)的新一代儀器總線,已經(jīng)成為業(yè)界開(kāi)放式總線的標(biāo)準(zhǔn),基于PX...

- 關(guān)鍵字: PXI LVDS 數(shù)字化儀模塊 FPGA

MathWorks發(fā)布在 MATLAB 和 Simulink中提供高級(jí)信號(hào)處理的新工具

- MathWorks面向使用MATLAB和Simulink設(shè)計(jì)高級(jí)信號(hào)處理和通信系統(tǒng)發(fā)布了重要的新功能。憑借常規(guī)的射頻子系統(tǒng)建模、高級(jí)電路包絡(luò)和諧波平衡分析方法,新的 SimRF 產(chǎn)品使系統(tǒng)架構(gòu)師可以使用 Simulink 來(lái)設(shè)計(jì)和驗(yàn)證完整的無(wú)線通信系統(tǒng)。對(duì)Simulink HDL Coder 進(jìn)行的一些重要更新,為自動(dòng) HDL 代碼生成添加了關(guān)鍵路徑分析和面積-速度優(yōu)化功能,以及輔助實(shí)現(xiàn) FPGA 全新的 Workflow Advisor。Communications Blockset、Signal

- 關(guān)鍵字: Simulink 高級(jí)信號(hào)處理 FPGA

dsp+fpga介紹

您好,目前還沒(méi)有人創(chuàng)建詞條dsp+fpga!

歡迎您創(chuàng)建該詞條,闡述對(duì)dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司