EEPW首頁(yè) >>

主題列表 >>

flash fpga

flash fpga 文章 最新資訊

基于FPGA的自適應(yīng)數(shù)字傳感器設(shè)計(jì)

- 摘要:高量程加速度傳感器在小信號(hào)的激勵(lì)下輸出在10 mV以內(nèi),傳統(tǒng)測(cè)試系統(tǒng)的噪聲可能覆蓋如此小的電壓信號(hào),使高量程的加速度傳感器無(wú)法測(cè)試小的加速度信號(hào)。針對(duì)這一問(wèn)題提出了基于自動(dòng)增益切換控制理論的自適應(yīng)數(shù)字

- 關(guān)鍵字: FPGA 數(shù)字 傳感器設(shè)計(jì)

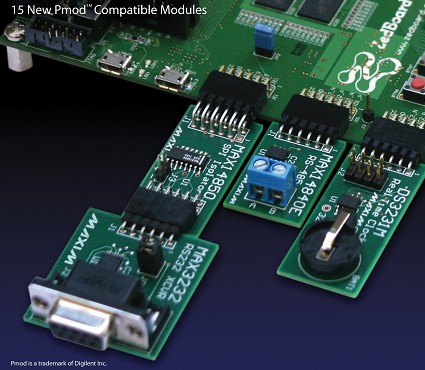

利用Maxim外設(shè)模塊加速FPGA原型設(shè)計(jì)、顯著降低成本

- Maxim Integrated Products (NASDAQ: MXIM)推出能夠直接插入符合Digilent? Pmod?標(biāo)準(zhǔn)的任意FPGA/CPU擴(kuò)展端口的15個(gè)外設(shè)模塊套裝。簡(jiǎn)單的連接操作和便利的軟件集成可加速原型開(kāi)發(fā)進(jìn)度,實(shí)現(xiàn)從概念至設(shè)計(jì)方案的快速移植。這套模塊的價(jià)格極具競(jìng)爭(zhēng)力,即使在預(yù)算最緊張的情況下,也可以采用先進(jìn)的高性能IC進(jìn)行方案測(cè)試。

- 關(guān)鍵字: Maxim FPGA

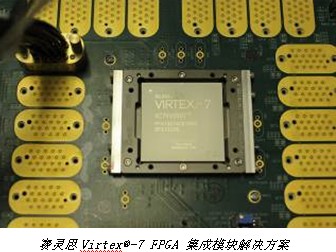

賽靈思推出符合PCI- E 3.0標(biāo)準(zhǔn)的集成模塊

- All Programmable FPGA、SoC和3D IC的全球領(lǐng)先企業(yè)賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX) )宣布推出針對(duì)采用Virtex?-7 FPGA 集成模塊設(shè)計(jì)的全新解決方案, 該集成模塊可支持PCI Express (簡(jiǎn)稱PCI-E) 3.0 x8標(biāo)準(zhǔn)和 DDR3 外部存儲(chǔ)器,能為開(kāi)發(fā)人員提供立即啟動(dòng)基于PCI-E 3.0的設(shè)計(jì)所需的全部構(gòu)建模塊。

- 關(guān)鍵字: 賽靈思 FPGA Virtex-7

基于高速串行BCD碼除法的數(shù)字頻率計(jì)的設(shè)計(jì)

- 摘要:介紹了在PPGA芯片上實(shí)現(xiàn)數(shù)字頻率計(jì)的原理。對(duì)各種硬件除法進(jìn)行了比較,提出了高速串行BCD碼除法的硬件算 ...

- 關(guān)鍵字: 頻率測(cè)量 周期測(cè)量 FPGA VHDL 狀態(tài)機(jī)

基于TMS320C6201DSP處理器與FLASH存儲(chǔ)器接口系統(tǒng)設(shè)計(jì)

- 電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術(shù)中心和交流中心,是電子產(chǎn)品的市場(chǎng)中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡(luò)家園

- 關(guān)鍵字: TMS320C6201 DSP Flash 存儲(chǔ)器接口

關(guān)于FLASH媒體報(bào)道的非官方辟謠

- 最近關(guān)于Flash的媒體報(bào)道真是越來(lái)越不靠譜了。這事兒本來(lái)就是內(nèi)行看門(mén)道,外行看熱鬧,之前一些媒體發(fā)的通過(guò)貶低Flash來(lái)肉麻吹捧HTML5的片面報(bào)道,我們大多數(shù)做過(guò)幾年Flash的開(kāi)發(fā)者都一笑了之了,懶得計(jì)較。 大家心里都有數(shù),兩個(gè)平臺(tái)各有優(yōu)缺點(diǎn),項(xiàng)目選型的時(shí)候,哪個(gè)合適就上哪個(gè)。就拿游戲來(lái)說(shuō),F(xiàn)lash還是占統(tǒng)治地

- 關(guān)鍵字: FLASH HTML5

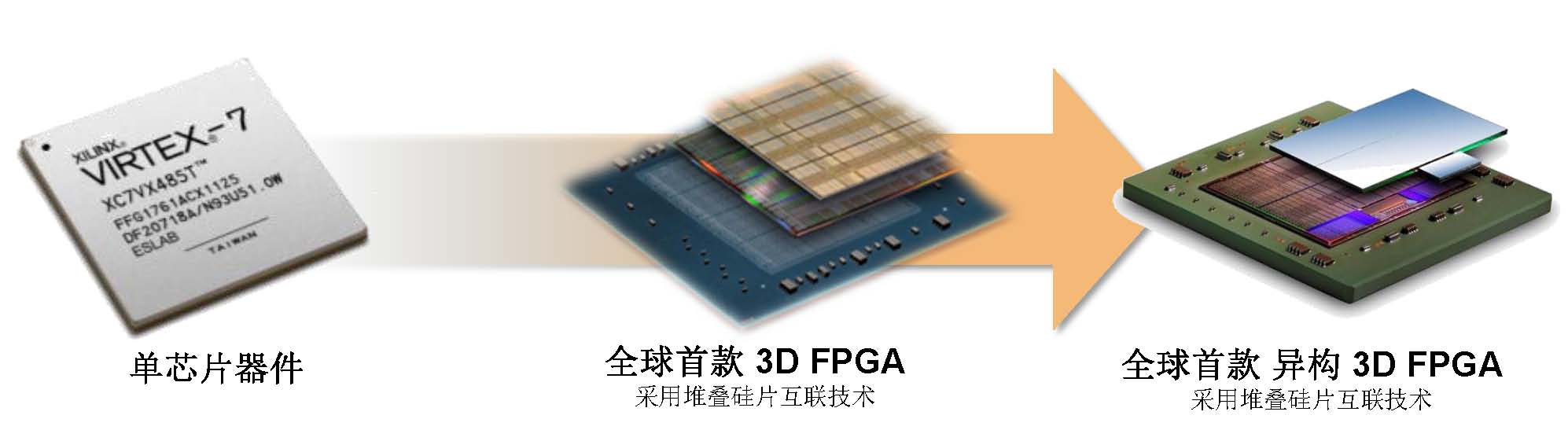

賽靈思異構(gòu)3D FPGA難在哪兒

- 不久前,All Programmable技術(shù)和器件的企業(yè)——賽靈思公司(Xilinx)正式發(fā)貨 Virtex-7 H580T FPGA—全球首款3D異構(gòu)All Programmable產(chǎn)品。 Virtex-7 HT采用賽靈思的堆疊硅片互聯(lián) (SSI)技術(shù),是提供業(yè)界帶寬最高的FPGA,可提供多達(dá)16個(gè)28 Gbps收發(fā)器和72個(gè)13.1 Gbps收發(fā)器,也是能滿足關(guān)鍵Nx100G和400G線路卡應(yīng)用功能要求的單芯片解決方案。 為此,本刊訪問(wèn)了該公司負(fù)責(zé)人,澄

- 關(guān)鍵字: Xilinx 賽靈思 3D FPGA all programmable 異構(gòu)

一種基于ARM和FPGA的可重構(gòu)MAC協(xié)議設(shè)計(jì)

- 一種基于ARM和FPGA的可重構(gòu)MAC協(xié)議設(shè)計(jì),摘要:為了在實(shí)際信道條件下研究Ad Hoc網(wǎng)絡(luò)MAC協(xié)議,克服商業(yè)網(wǎng)卡芯片和理論仿真等帶來(lái)的局限性,搭建了基于ARM和FPGA相結(jié)合的硬件平臺(tái),設(shè)計(jì)與實(shí)現(xiàn)了基于CSMA/CA的可重構(gòu)MAC協(xié)議,并進(jìn)行了仿真測(cè)試,驗(yàn)證了該協(xié)議設(shè)

- 關(guān)鍵字: 協(xié)議 設(shè)計(jì) MAC 重構(gòu) ARM FPGA 基于

基于FPGA和FLASH ROM的圖像信號(hào)發(fā)生器設(shè)計(jì)

- 摘要:以XC2V1500-FPGA為硬件架構(gòu),設(shè)計(jì)了一種圖像信號(hào)發(fā)生器,作為自適應(yīng)光學(xué)系統(tǒng)波前處理機(jī)的信號(hào)源,為波前處理機(jī)的調(diào)試和算法驗(yàn)證提供支持。系統(tǒng)采用大容量的NAND型FLASH存儲(chǔ)數(shù)據(jù),存儲(chǔ)容量為1 GB。圖像數(shù)據(jù)通過(guò)

- 關(guān)鍵字: FLASH FPGA ROM 圖像信號(hào)發(fā)生器

單片機(jī)與FPGA實(shí)現(xiàn)等精度頻率測(cè)量和IDDS技術(shù)設(shè)計(jì)方案

- O.引言本系統(tǒng)利用單片機(jī)和FPGA有效的結(jié)合起來(lái)共同實(shí)現(xiàn)等精度頻率測(cè)量和IDDS技術(shù),發(fā)揮各自的優(yōu)點(diǎn),使設(shè)計(jì)變得 ...

- 關(guān)鍵字: 單片機(jī) FPGA 頻率測(cè)量 IDDS技術(shù)

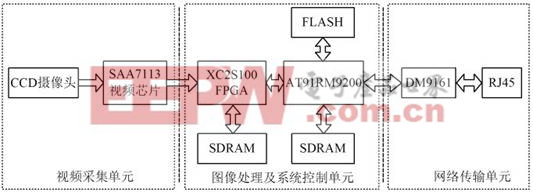

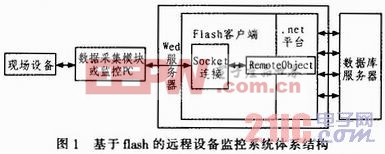

基于Flash的遠(yuǎn)程工業(yè)監(jiān)控系統(tǒng)設(shè)計(jì)

- 摘要:根據(jù)當(dāng)前基于Web遠(yuǎn)程工業(yè)監(jiān)控方案的不足,利用Flash的交互性強(qiáng),本身導(dǎo)出的文件小,適合網(wǎng)絡(luò)傳輸、利用AS(Action Script)提高了與其他語(yǔ)言的交互性等特點(diǎn),提出了基于Flash的遠(yuǎn)程工業(yè)監(jiān)控系統(tǒng)設(shè)計(jì)思路。提出了

- 關(guān)鍵字: 監(jiān)控系統(tǒng) 設(shè)計(jì) 工業(yè) 遠(yuǎn)程 Flash 基于

flash fpga介紹

您好,目前還沒(méi)有人創(chuàng)建詞條flash fpga!

歡迎您創(chuàng)建該詞條,闡述對(duì)flash fpga的理解,并與今后在此搜索flash fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)flash fpga的理解,并與今后在此搜索flash fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司