EEPW首頁(yè) >>

主題列表 >>

fpga ip

fpga ip 文章 最新資訊

Altera發(fā)售業(yè)界密度最高的收發(fā)器FPGA

- Altera公司(NASDAQ: ALTR)今天宣布,開始提供業(yè)界密度最高的收發(fā)器FPGA芯片。作為Altera® Stratix® IV GX FPGA系列中發(fā)售的第二個(gè)型號(hào)器件,EP4SGX530比市場(chǎng)上最大的收發(fā)器FPGA大60%。該器件提供530K邏輯單元(LE),48個(gè)工作速率高達(dá)8.5 Gbps的收發(fā)器,20.3 Mbits RAM以及1,040個(gè)嵌入式乘法器。Stratix IV GX器件面向通信、廣播、測(cè)試、醫(yī)療和軍事市場(chǎng)等多種應(yīng)用領(lǐng)域。 Agilent邏輯和協(xié)議

- 關(guān)鍵字: Altera,F(xiàn)PGA,收發(fā)器

安森美半導(dǎo)體將提供用于標(biāo)準(zhǔn)接口、微控制器及外設(shè)的新IP模塊,

- 2009年3月17日 - 全球領(lǐng)先的高性能、高能效硅解決方案供應(yīng)商安森美半導(dǎo)體(ON Semiconductor,美國(guó)納斯達(dá)克上市代號(hào):ONNN)擴(kuò)充知識(shí)產(chǎn)權(quán)(IP)陣容,添增超過30項(xiàng)經(jīng)過硅驗(yàn)證的IP模塊。客戶采用基于安森美半導(dǎo)體數(shù)字和混合信號(hào)工藝技術(shù)開發(fā)專用集成電路(ASIC)和系統(tǒng)級(jí)芯片(SoC)如今將可獲得更多的IP,用于行業(yè)標(biāo)準(zhǔn)接口、微控制器及外設(shè)。 這些新IP適合于運(yùn)營(yíng)在不同行業(yè)及應(yīng)用領(lǐng)域的客戶,包括軍事及航空、網(wǎng)絡(luò)及無線通信、消費(fèi)電子、汽車和工業(yè)自動(dòng)化。添增到安森美半導(dǎo)體IP陣

- 關(guān)鍵字: 安森美 IP 行業(yè)標(biāo)準(zhǔn)接口 微控制器 外設(shè)

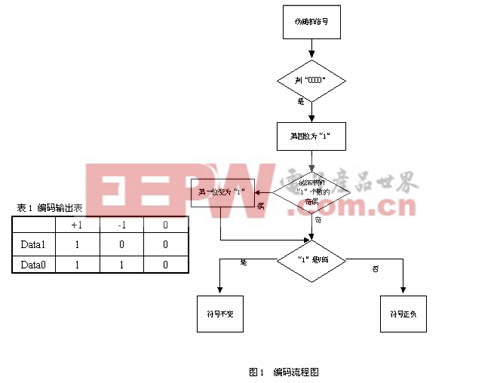

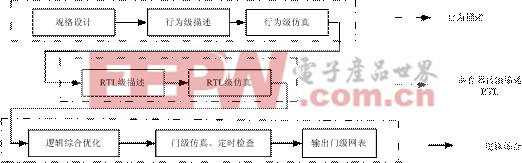

基于FPGA的無線通信收發(fā)模塊設(shè)計(jì)方案

- 1 前言 近年來,隨著半導(dǎo)體工藝技術(shù)和設(shè)計(jì)方法的迅速發(fā)展,系統(tǒng)級(jí)芯片SOC的設(shè)計(jì)得以高速發(fā)展,這已成為業(yè)界熱點(diǎn)。但是,由于SOC產(chǎn)品設(shè)計(jì)具有開發(fā)周期相對(duì)較長(zhǎng)、高成本和高風(fēng)險(xiǎn)等特點(diǎn),對(duì)市場(chǎng)的變化非常敏感,這使

- 關(guān)鍵字: 設(shè)計(jì) 方案 模塊 收發(fā) FPGA 無線通信 基于 FPGA 無線通信收發(fā)模塊 設(shè)計(jì)方案 摩爾斯碼

基于FPGA的高速數(shù)據(jù)中繼器設(shè)計(jì)的研究

- 1 前言 高速以太網(wǎng)可以滿足新的容量需求,解決了低帶寬接入、高帶寬傳輸?shù)钠款i問題,擴(kuò)大了應(yīng)用范圍,并與以前的所有以太網(wǎng)兼容。全雙工的以太網(wǎng)協(xié)議并無傳輸距離的限制,只是在實(shí)際應(yīng)用中,物理層技術(shù)限制了最

- 關(guān)鍵字: FPGA 高速數(shù)據(jù) 中繼器

用FPGA實(shí)現(xiàn)靈活的汽車電子設(shè)計(jì)

- 引言 微控制器在汽車和消費(fèi)類市場(chǎng)上得到了廣泛應(yīng)用,能夠以相對(duì)較低的成本實(shí)現(xiàn)系統(tǒng)高度集成。然而,這類產(chǎn)品也有潛在的成本問題。例如,如果元件功能不符合要求,就必須采用外部邏輯、軟件或者其他集成器件

- 關(guān)鍵字: FPGA 汽車 電子設(shè)計(jì)

基于單片機(jī)和FPGA的頻率特,tt測(cè)試儀

- 介紹基于89S51單片機(jī)和FPGA的頻率特性測(cè)試儀的設(shè)計(jì)。該系統(tǒng)設(shè)計(jì)利用DDS原理由FPGA經(jīng)D/A轉(zhuǎn)換產(chǎn)生掃頻信號(hào),再經(jīng)待測(cè)網(wǎng)絡(luò)實(shí)現(xiàn)峰值檢測(cè)和相位檢測(cè),從而完成了待測(cè)網(wǎng)絡(luò)幅頻和相頻特性曲線的測(cè)量和顯示。經(jīng)過調(diào)試,示波器顯示待測(cè)網(wǎng)絡(luò)頻率范圍100 Hz~100 kHz的幅頻和相頻特性曲線,該系統(tǒng)工作穩(wěn)定,操作方便。

- 關(guān)鍵字: tt 測(cè)試儀 頻率 FPGA 單片機(jī) 基于 轉(zhuǎn)換器

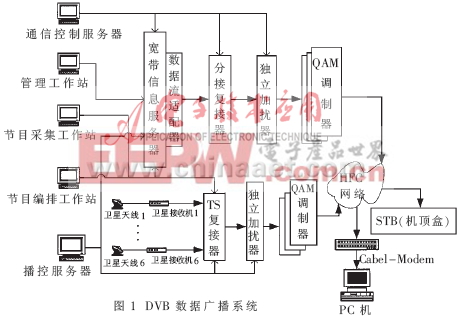

一種寬帶復(fù)接器的設(shè)計(jì)與實(shí)現(xiàn)

- 信息時(shí)代的到來使人們需要共享越來越多的信息。隨著信息及其需求的爆炸性增長(zhǎng),信息的選擇及傳輸速率成為一個(gè)重要問題。有線電視網(wǎng)絡(luò)有其固有的高帶寬特性,適合大容量的數(shù)據(jù)傳輸和實(shí)時(shí)性要求,使寬帶數(shù)字接入成為可能。

- 關(guān)鍵字: 實(shí)現(xiàn) 設(shè)計(jì) 寬帶 DVB-C數(shù)據(jù)廣播 TS復(fù)接器 DSP FPGA 網(wǎng)絡(luò)

基于FPGA 的簡(jiǎn)化UART 電路設(shè)計(jì)

- 摘要: 本文闡述了通用異步發(fā)生器UART 的功能特點(diǎn),介紹了用硬件描述語(yǔ)言Verilog 來開發(fā)各個(gè)模塊,并給出仿真結(jié)果。本設(shè)計(jì)使用Altera 的FPGA 芯片,將UART 的核心功能嵌入到FPGA 內(nèi)部,能夠?qū)崿F(xiàn)異步通信的功能,可以

- 關(guān)鍵字: FPGA UART 電路設(shè)計(jì)

fpga ip介紹

您好,目前還沒有人創(chuàng)建詞條fpga ip!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司