EEPW首頁(yè) >>

主題列表 >>

fpga soc

fpga soc 文章 最新資訊

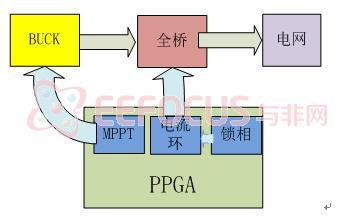

基于FPGA 的太陽(yáng)能并網(wǎng)逆變器的研究

- 系統(tǒng)概述 新能源發(fā)電成為21世紀(jì)解決能源危機(jī)的必經(jīng)出路,光伏發(fā)電、風(fēng)電、核電等新能源發(fā)電是目前新能源發(fā)電研究的幾大方向。這幾種新能源各有各的特點(diǎn),我們選擇了最靠近我們的光伏發(fā)電作為研究出發(fā)點(diǎn)。 目前光伏發(fā)電并網(wǎng)技術(shù)的研究愈加深入成熟,而關(guān)于光伏發(fā)電技術(shù)的具體應(yīng)用環(huán)節(jié)還是有著許多發(fā)揮余地。光伏發(fā)電的優(yōu)點(diǎn)是清潔安全、分布相對(duì)較為均勻、可持續(xù)利用。同時(shí)光伏發(fā)電也存在自己的問(wèn)題,其中一個(gè)很重要的問(wèn)題是光伏發(fā)電需要做的是收集輻射到地表的太陽(yáng)能,這個(gè)環(huán)節(jié)需要占用大量的空間,這個(gè)問(wèn)題使光伏發(fā)電的應(yīng)用有著

- 關(guān)鍵字: FPGA 逆變器

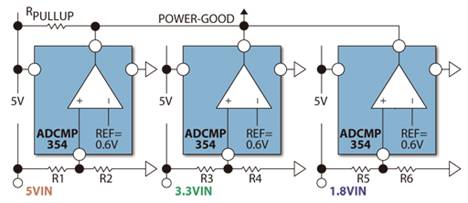

混合信號(hào)IC──復(fù)雜電源管理組件的設(shè)計(jì)挑戰(zhàn)及解決方案

- 隨著系統(tǒng)內(nèi)電源數(shù)量的增多,為了確保其安全、經(jīng)濟(jì)、持續(xù)和正常的工作,對(duì)電源軌進(jìn)行監(jiān)測(cè)和控制變得非常重要,特別是在使用微處理器時(shí)。確定電壓軌是否處于工作范圍內(nèi),以及該電壓相對(duì)于其它電壓軌是否按照正確的時(shí)序上電或斷電,這些對(duì)于系統(tǒng)執(zhí)行的可靠性和安全性來(lái)說(shuō)都是至關(guān)重要的。例如FPGA,在向組件提供5V I/O(輸入/輸出)電壓之前,必須先施加3.3V的核心電壓,并持續(xù)至少20ms,以避免組件上電時(shí)受到損壞。對(duì)于系統(tǒng)的可靠性來(lái)說(shuō),滿足這樣的時(shí)序要求就像要保證組件在規(guī)定的電源電壓和溫度范圍內(nèi)工作一樣至關(guān)重要。

- 關(guān)鍵字: FPGA DSP

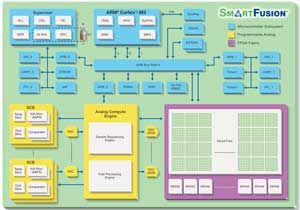

混合信號(hào)FPGA實(shí)現(xiàn)真正單芯片SOC

- 要實(shí)現(xiàn)能夠?qū)⑺兄匾δ芗稍趩我黄骷脑O(shè)計(jì)理由很簡(jiǎn)單,因?yàn)檫@樣就能將材料成本、部件庫(kù)存及電路板面積減至最低。另外,相較于多芯片解決方案,單芯片方案的功耗也較低,同時(shí)也有助于提高對(duì)知識(shí)產(chǎn)權(quán)的保護(hù)。如果一項(xiàng)設(shè)計(jì)功能的精髓能夠深植于單一芯片上,將會(huì)大大增加第三方取得這項(xiàng)設(shè)計(jì)的困難度。 單芯片系統(tǒng)對(duì)嵌入式系統(tǒng)設(shè)計(jì)師來(lái)說(shuō),往往會(huì)隨著其面對(duì)的不同的系統(tǒng)設(shè)計(jì)而各有不同。例如,在龐大的娛樂(lè)或通信消費(fèi)產(chǎn)品市場(chǎng)中,SoC意味著一顆具有數(shù)百萬(wàn)邏輯門(mén)的集成電路(IC),其中包含許多大型定制邏輯模塊,并有將芯片的數(shù)字處

- 關(guān)鍵字: FPGA SOC

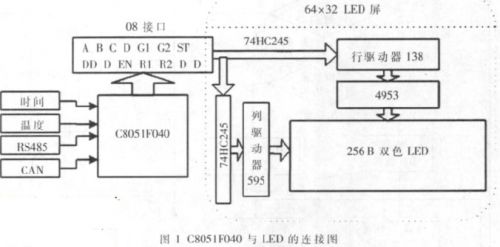

混合信號(hào)SoC在雙色LED屏中的應(yīng)用

- 1 高速SoC單片機(jī)C8051F040特征 C8051F040系列器件是完全集成的混合信號(hào)片上系統(tǒng)型MCU,具有64個(gè)數(shù)字I/O 引腳,片內(nèi)集成了1個(gè)CAN2.0B控制器。其主要特性有: (1)高速流水線結(jié)構(gòu)的8051兼容的CIP-51內(nèi)核(可達(dá)25 MIPS);(2)全速非侵入式的在系統(tǒng)調(diào)試接口(片內(nèi)) 64 KB(C8051F040/1/2/3/4/5)可在系統(tǒng)編程的Flash存儲(chǔ)器,(4K+256)B的片內(nèi)RAM,尋址空間為64 KB的外部數(shù)據(jù)存儲(chǔ)器接口和硬件實(shí)現(xiàn)的SPI、SMBus/I2

- 關(guān)鍵字: SoC LED

Synopsys宣布推出用于移動(dòng)SoC的業(yè)界最低功耗PCI Express 3.1 IP解決方案

- 新思科技(Synopsys,Inc)日前宣布:推出業(yè)界功耗最低的、兼容PCI Express®(PCIe®)3.1規(guī)范的控制器和PHY知識(shí)產(chǎn)權(quán)(IP)解決方案,它們可以同時(shí)極大地降低移動(dòng)系統(tǒng)級(jí)芯片(SoC)的工作和待機(jī)功耗。經(jīng)硅驗(yàn)證的Synopsys DesignWare® PCIe 3.1 IP支持L1低功耗狀態(tài),并采用電源開(kāi)關(guān)、分段電源層以及低待機(jī)功耗等電源門(mén)控技術(shù),使待機(jī)功耗低于10 uW/lane。此外,正常供電時(shí),這種新型發(fā)送器設(shè)計(jì)和均衡旁路方案使工作功耗低于5mW/

- 關(guān)鍵字: Synopsys SoC

Mentor Graphics 宣布推出旨在提升測(cè)試平臺(tái)效率的 EZ-VIP 包

- Mentor Graphics公司今天宣布即時(shí)推出 EZ-VIP 效率包。該效率包面向使用 Questa® Verification IP (QVIP) 的 ASIC 和 FPGA 驗(yàn)證團(tuán)隊(duì),可將創(chuàng)建、實(shí)例化、配置和連接 QVIP 測(cè)試平臺(tái)的時(shí)間縮短 5 倍以上,從而顯著提高效率。這就意味著,驗(yàn)證團(tuán)隊(duì)可以將更多的時(shí)間花在 QVIP 上,以驗(yàn)證他們的設(shè)計(jì)在功能上是否正確。 EZ-VIP 包由 QVIP 配置軟件、一個(gè) VIP 調(diào)通服務(wù)包和一個(gè)全新的 EZ-VIP API 組成。其中,QVI

- 關(guān)鍵字: Mentor Graphics FPGA

【從零開(kāi)始走進(jìn)FPGA】 玩轉(zhuǎn)VGA

- 一、VGA的誘惑 首先,VGA的驅(qū)動(dòng),這事,一般的單片機(jī)是辦不到的;由于FPGA的速度,以及并行的優(yōu)勢(shì),加上可現(xiàn)場(chǎng)配置的優(yōu)勢(shì),VGA的配置,只有俺們FPGA可以勝任,也只有FPGA可以隨心所欲地配置(當(dāng)然ARM也可以,應(yīng)用比較高吧)。 初學(xué)者就是喜歡看炫的效果,往往會(huì)忍不住想玩。尤其玩FPGA的,沒(méi)玩VGA就感到跟單片機(jī)沒(méi)啥提升,因此VGA的驅(qū)動(dòng)也不得不講。Bingo當(dāng)年也是如此。擋不住VGA的誘惑,初學(xué)者問(wèn)Bingo VGA問(wèn)題的人也是灰常的多,也許一般教科書(shū)理論太強(qiáng),實(shí)際應(yīng)用不是很身后

- 關(guān)鍵字: VGA FPGA

Altera宣布Stratix 10的創(chuàng)新全面刷新高端FPGA和SoC業(yè)界性能指標(biāo)記錄

- Altera公司今天發(fā)布其Stratix® 10 FPGA和SoC體系結(jié)構(gòu)和產(chǎn)品細(xì)節(jié),這一下一代高端可編程邏輯器件在性能、集成度、密度和安全特性方面實(shí)現(xiàn)全面突破,勢(shì)必將云時(shí)代的網(wǎng)絡(luò)通信技術(shù)推向又一個(gè)巔峰。 Stratix 10 FPGA和SoC采用了Altera革命性的HyperFlex™ FPGA架構(gòu),由Intel® 14 nm三柵極工藝技術(shù)制造,內(nèi)核性能是前一代FPGA的2倍。業(yè)界性能最好、密度最高、具有先進(jìn)的嵌入式處理功能的FPGA與GPU級(jí)別浮點(diǎn)計(jì)算性能和異構(gòu)

- 關(guān)鍵字: Altera FPGA

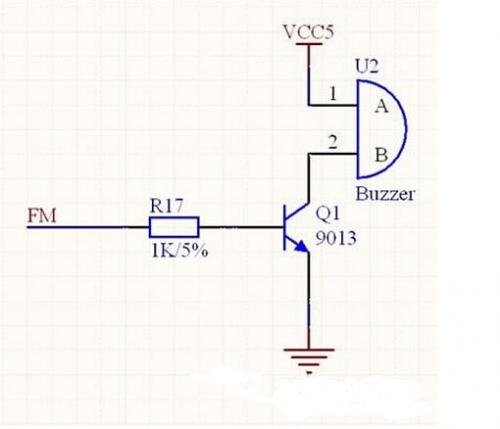

FPGA開(kāi)發(fā)外設(shè)子板模塊電路設(shè)計(jì)詳解

- FPGA(Field-Programmable Gate Array),即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門(mén)電路數(shù)有限的缺點(diǎn)。FPGA的開(kāi)發(fā)相對(duì)于傳統(tǒng)PC、單片機(jī)的開(kāi)發(fā)有很大不同。FPGA以并行運(yùn)算為主,以硬件描述語(yǔ)言來(lái)實(shí)現(xiàn);相比于PC或單片機(jī)(無(wú)論是馮諾依曼結(jié)構(gòu)還是哈佛結(jié)構(gòu))的順序操作有很大區(qū)別,也造成了FPGA開(kāi)發(fā)入門(mén)較難。目前國(guó)內(nèi)有專

- 關(guān)鍵字: FPGA A/D

非接觸式讀卡器設(shè)計(jì)方案匯總,包括RFID,磁卡等

- 讀卡器(Card Reader)是一種讀卡設(shè)備,由于卡片種類較多,所以讀卡器的含義覆蓋范圍比較廣。根據(jù)卡片類型的不同,可以將其分為IC卡讀卡器,包括接觸式IC卡,遵循ISO7816接口標(biāo)準(zhǔn);非接觸式IC卡讀卡器,遵循ISO14443接口標(biāo)準(zhǔn),遠(yuǎn)距離讀卡器,遵循ETC國(guó)標(biāo)GB20851接口標(biāo)準(zhǔn)。本文主要介紹非接觸式讀卡器的設(shè)計(jì)方案,供大家參考。 一種極具成本效益的磁卡讀卡器設(shè)計(jì) 通過(guò)磁性圖案存儲(chǔ)信息的技術(shù)最早出現(xiàn)在音頻記錄領(lǐng)域。從那以后,這個(gè)概念已被擴(kuò)展應(yīng)用于許多不同產(chǎn)品,如軟盤(pán)、音頻/視頻

- 關(guān)鍵字: SOC PICl6F7x

基于FPGA的915MHz射頻讀卡器設(shè)計(jì)

- 射頻識(shí)別(RFID)技術(shù)是一種非接觸式的自動(dòng)識(shí)別技術(shù),通過(guò)射頻信號(hào)自動(dòng)識(shí)別目標(biāo)對(duì)象并獲取相關(guān)信息。通常RFID系統(tǒng)主要由應(yīng)用軟件、射頻卡以及讀卡器三部分構(gòu)成[1]。相對(duì)于低頻段的RFID系統(tǒng),工作在860 MHz~960 MHz的超高頻段(UHF)RFID系統(tǒng)有著讀取距離遠(yuǎn)、閱讀速度快等優(yōu)點(diǎn),是目前國(guó)際上RFID技術(shù)發(fā)展的熱點(diǎn)[2]。讀卡器的設(shè)計(jì)是RFID系統(tǒng)設(shè)計(jì)中的關(guān)鍵部分,設(shè)計(jì)方案有很多種。FPGA[3]具有開(kāi)發(fā)簡(jiǎn)單、靜態(tài)可重復(fù)編程和動(dòng)態(tài)在線編程的特點(diǎn),已經(jīng)成為當(dāng)今應(yīng)用最廣泛的可編程專用集成電路。

- 關(guān)鍵字: FPGA 讀卡器

FPGA的系統(tǒng)架構(gòu)組成和器件互聯(lián)問(wèn)題

- 通常來(lái)講,“一個(gè)好漢三個(gè)幫”,一個(gè)完整的嵌入式系統(tǒng)中由單獨(dú)一個(gè)FPGA使用的情況較少。通常由多個(gè)器件組合完成,例如由一個(gè)FPGA+CPU來(lái)構(gòu)成。通常為一個(gè)FPGA+ARM,ARM負(fù)責(zé)軟件配置管理,界面輸入外設(shè)操作等操作,F(xiàn)PGA負(fù)責(zé)大數(shù)據(jù)量運(yùn)算,可以看做CPU的專用協(xié)處理器來(lái)使用,也常會(huì)用于擴(kuò)展外部接口。常用的有ARM+FPGA,DSP+FPGA,或者網(wǎng)絡(luò)處理器+FPGA等種種架構(gòu)形式,這些架構(gòu)形式構(gòu)成整個(gè)高速嵌入式設(shè)備的處理形態(tài)。 不得不說(shuō)的是,隨著技術(shù)的進(jìn)步,現(xiàn)在CP

- 關(guān)鍵字: ARM FPGA

fpga soc介紹

您好,目前還沒(méi)有人創(chuàng)建詞條fpga soc!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司