- 多處理器系統已廣泛應用于高速信號處理領域,為提高系統性能,更好地發揮多處理器優勢,介紹采用基于FPGA的多DSF架構。利用FPGA作為數據調度核心,將處理器從繁雜的數據通信工作中解放出來,充分發揮了多處理器的并行工作能力,增強了系統的重構和拓展性。該系統已應用于工程實踐中,以一塊高密度電路板實現了從數據采集到圖像校正、圖像處理,以及圖像顯示的整個流程,能夠滿足對處理時間要求較高、較為復雜的圖像處理算法的要求。

- 關鍵字:

FPGA DSP 紅外 處理系統

- 摘要:給出了一種基于多相濾波的數字信道化接收機的實現方法,系統的處理帶寬為875 MHz,解決了高速ADC與FPGA處理速度之間的矛盾。為了克服信道化接收機的接收盲區,采用信道重疊的方法,連續覆蓋瞬時帶寬。在信道化

- 關鍵字:

FPGA 多相濾波 數字接收機

- 全球可編程平臺領導廠商賽靈思公司(Xilinx, Inc)宣布收購高層綜合技術領先公司美國AutoESL設計科技有限公司。

通過增加高層綜合技術,賽靈思進一步擴展了其技術基礎和產品組合,使得公司能夠把可編程平臺的優勢帶給更廣泛的企業用戶群體,即那些習慣用 C、C++ 和 System C 語言進行高層抽象設計的系統架構師和硬件設計人員。同時,這也將使得賽靈思可以滿足客戶對工具日益提高的需求,支持電子系統級 (ESL) 設計方法,滿足當今現場可編程門陣列 (FPGA) 領域復雜的設計需求。

- 關鍵字:

賽靈思 FPGA

- 摘要:為提高安防措施,延緩不法分子動作,確保營區安全,提出一種營區智能防沖擊系統解決方案。該方案以移動物體的外形形狀、車牌信息、車輛速度為輸入特征,采用虛擬線圈感應、車牌識別、車輛測速、系統控制等方法

- 關鍵字:

FPGA 系統設計

- 摘要:設計了基于FPGA和NioslI軟核的全數字逆變焊接電源控制器,采用變參數PID和改進的I-I型雙閉環電流-弧長控制策略,并應用于數字化MIG焊接電源系統中。介紹了該電源控制器各模塊的功能及設計方案,分析了MIG焊接電

- 關鍵字:

NiosII FPGA 逆變焊接 電源控制器

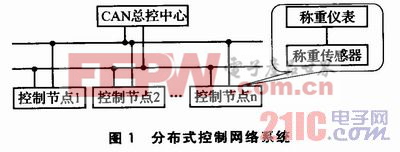

- 摘要:根據CAN總線的特性,給出了基于Cortex-M3內核的LM3S2965芯片中CAN總線節點的硬件電路、軟件實現框架及部分代碼。初始化代碼部分可以直接應用在其他CAN總線的接口設計中。

關鍵詞:CAN;Cortex-M3;稱重儀表;

- 關鍵字:

LED ARM Cortex-M3 控制器 通信

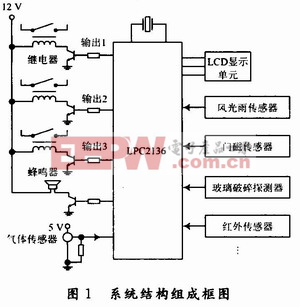

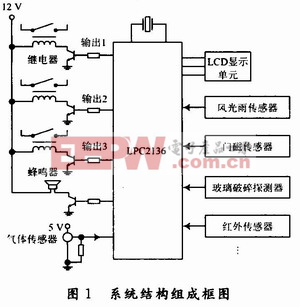

- 基于嵌入式系統的智能門窗設計,為了使家居生活更加舒適、安全,采用以ARM7為主控制芯片,融合多路傳感器的方法,突破了傳統的防盜門窗模式。綜合考慮了室內外環境的安全因素,設計了一種基于嵌入式系統的智能門窗,進行了以CO、煤氣、甲醛以及風光雨傳感器為主要信號獲取單元,以聲光報警器、排風扇和電動開窗器為執行機構的聯合調試實驗設計,實驗中系統運行穩定可靠。實驗結果證明該設計切實可行。

- 關鍵字:

ARM

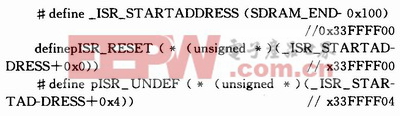

- ARM-Linux嵌入式系統的Boot Loader分析與設計,Boot Loader作為ARM嵌入式系統的一個重要部分。對于使用不相同版本的內核的系統板,所時應的Boot Loader也是相同,因此對每個系統板都要對其運行其所對應的Boot Loader。在此簡要介紹S3C2410及其兩種啟動方式,著重分析S3C2410從NANDFLASH啟動的過程中,對各個內部功能模塊進行初始化過程,并設計出基于S3C2410嵌入式系統的Boot Loader。通過在線仿真及實際測試表明,該Boot Loader具有

- 關鍵字:

ARM

- 為了給實際應用中選擇合適FIR濾波器的FPGA實現結構提供參考,首先從FIR數字濾波器的基本原理出發,分析了FIR濾波器的結構特點,然后分別介紹了基于FPGA的FIR濾波器的串行、并行、轉置型、FFT型和分布式結構型的實現方法,對于各種實現的結構做了分析、比較以及優化處理,特別是對基于FFT的FIR濾波器與傳統卷積結構進行了精確的數值計算比較,最后得出滿足于低階或高階的各種FIR濾波器實現結構的適用范圍及其優缺點,并針對實際工程應用提出了下一步需解決的問題。

- 關鍵字:

FPGA FIR 濾波器 實現方法

- ARM在控制住移動芯片市場的同時,計劃在芯片權限市場再出擊,該公司計劃到2015年將在PC和服務器市場取得立足點。

該消息是出自本周早些時候ARM的盈利分析電話會議。ARM公司基本上也是一個芯片技術授權公司。因此,這對于它來說是一個極大的優勢,因為他們并不需要自己生產和加工處理器芯片。相反,像Nvidia這樣的芯片公司,則要在對芯片進行設計的同時加工和制造芯片產品。不過,可以肯定的是這條信息的意義是明確的。ARM很明顯的想要進駐到PC和服務器市場,成為其中的選手,在2011年美國舉辦的CES展會

- 關鍵字:

ARM 服務器芯片

- 通過對現有編碼算法的改進,提出一種新的編碼算法,它降低功耗的方法是通過減少部分積的數量來實現的。因為乘法器的運算主要是部分積的相加,因此,減少部分積的數量可以降低乘法器中加法器的數量,從而實現功耗的減低。在部分積的累加過程中.又對用到的傳統全加器和半加器進行了必要的改進,避免了CMOS輸入信號不必要的翻轉,從而降低了乘法器的動態功耗。通過在Altera公司的FPGA芯片EP2CTOF896C中進行功耗測試,給出了測試結果,并與現有的兩種編碼算法進行了比較。功耗分別降低3.5%和8.4%。

- 關鍵字:

FPGA 24位 低功耗 乘法器

fpga+arm介紹

您好,目前還沒有人創建詞條fpga+arm!

歡迎您創建該詞條,闡述對fpga+arm的理解,并與今后在此搜索fpga+arm的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473