fpga+mpu+mcu 文章 最新資訊

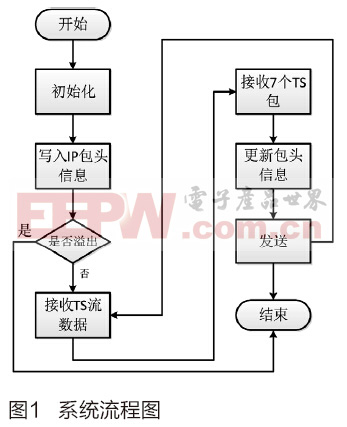

基于FPGA的TS over IP的設計與實現(xiàn)

- 隨著互聯(lián)網(wǎng)的發(fā)展, 數(shù)字電視信號的網(wǎng)絡傳輸?shù)玫搅嗽絹碓蕉嗟年P注,本文設計與實現(xiàn)了一種基于FPGA和MCU(R8051XC2)的TS over IP系統(tǒng),并對傳統(tǒng)的TS over IP系統(tǒng)進行了改進。此系統(tǒng)通過從標準TS流接口接收TS流,將其以乒乓操作的方式存放在兩個雙口RAM中,再通過一定方法封裝IP包發(fā)送至網(wǎng)絡,實現(xiàn)了TS流和網(wǎng)絡IP數(shù)據(jù)包的相互轉換。通過向系統(tǒng)推送TS流數(shù)據(jù)并使用抓包軟件對經過系統(tǒng)的數(shù)據(jù)進行分析統(tǒng)計的方法證明,得出以下結論,此系統(tǒng)在相同情況與有限的硬件條件下,相比傳統(tǒng)的使用FIFO作為

- 關鍵字: FPGA TS over IP 異步時鐘域通信 雙端口RAM 201509

神級經典設計案例:用ARM和FPGA搭建神經網(wǎng)絡處理器通信方案

- 引言 人工神經網(wǎng)絡在很多領域得到了很好的應用,尤其是具有分布存儲、并行處理、自學習、自組織以及非線性映射等特點的網(wǎng)絡應用更加廣泛。嵌入式便攜設備也越來越多地得到應用,多數(shù)是基于ARM內核及現(xiàn)場可編程門陣列FPGA的嵌入式應用。某人工神經網(wǎng)絡的FPGA處理器能夠對數(shù)據(jù)進行運算處理,為了實現(xiàn)集數(shù)據(jù)通信、操作控制和數(shù)據(jù)處理于一體的便攜式神經網(wǎng)絡處理器,需要設計一種基于嵌入式ARM內核及現(xiàn)場可編程門陣列FPGA的主從結構處理系統(tǒng)滿足要求。 1人工神經網(wǎng)絡處理器 1.1人工神經網(wǎng)絡模型

- 關鍵字: ARM FPGA

低功耗軟件開發(fā)延長電池使用壽命

- 電池技術的創(chuàng)新并不像其它技術優(yōu)勢那樣迅速。每隔十年,電池容量就會增加一倍,同時市場對于電池工藝的要求也越來越高,這給電池開發(fā)人員帶來了許多艱巨的挑戰(zhàn)。電池開發(fā)人員在設計電池供電系統(tǒng)時經常會發(fā)現(xiàn),雖然系統(tǒng)硬件的效率提高了,但電池的功耗卻往往比預期高出很多。實際上,在優(yōu)化嵌入式系統(tǒng)時,硬件只是必須考慮的因素之一,另一個不可或缺的因素則是軟件。 如果電池開發(fā)人員希望電池發(fā)揮最佳性能,可以通過管理微控制器 (MCU) 軟件的方法來解決。在著手開始之前,不妨先參考以下技巧: 1. 盡可能增加MCU待

- 關鍵字: MCU 低功耗

點燃產業(yè)創(chuàng)新之火,ICChina推動FPGA鼓勵創(chuàng)新

- 在今天,創(chuàng)新能力是個熱門話題。各個國家在戰(zhàn)略、政策上對此也高度重視。今年,國務院印發(fā)《中國制造2025》明確提出提高國家制造業(yè)創(chuàng)新能力。今天,創(chuàng)新式思維對于所有工程領域的技術人員變得如此重要。這主要是全球范圍的技術進步所帶來的壓力,競爭已經是在全球范圍了。發(fā)明創(chuàng)造是每個工程技術人員的夢想,而創(chuàng)新思維是發(fā)明創(chuàng)造的第一步。創(chuàng)新思維是我們大腦在產生新思想或新概念的一個過程,也可以是對現(xiàn)存思想和概念新的延續(xù)。在電子工程領域,F(xiàn)PGA在培養(yǎng)和教育新一代工程技術人員的創(chuàng)新思維中扮演著重要角色。 ICChin

- 關鍵字: ICChina FPGA

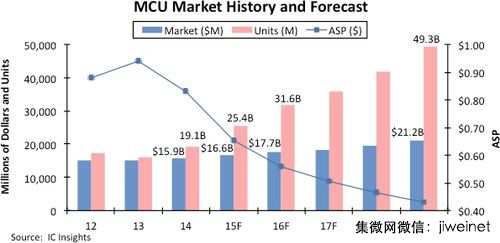

ASP持續(xù)下跌 MCU市場成長受限

- 隨著越來越多的電子業(yè)者不斷為物聯(lián)網(wǎng)(IoT)推出新產品,全球微控制器(MCU)市場出貨量正出現(xiàn)巨大成長動能。然而,根據(jù)市場研究公司IC Insights表示,近期前所未有的市場價格走跌趨勢,也意味著MCU供應商只能看到銷售額的微幅增加。 在IC Insights發(fā)布的最新McClean報告中提到,由于近來針對智慧卡與32位元應用的MCU單位量大幅激增(其中有許多都瞄準了IoT),預計今年的MCU出貨量將持續(xù)穩(wěn)定增加33%,達到254億顆單位。但來自MCU的整體營收預計只會增加4%,達到166億美

- 關鍵字: ASP MCU

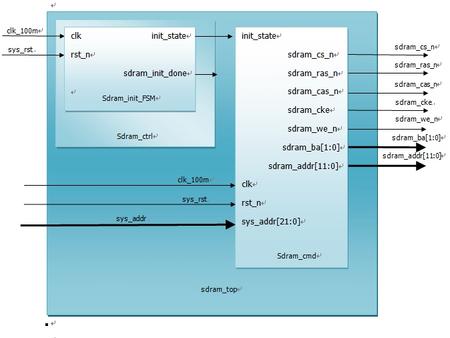

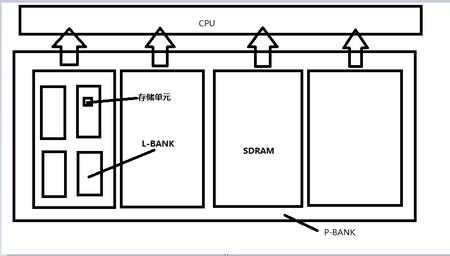

零基礎學FPGA (二十五)必會! 從靜態(tài)時序分析到SDRAM時序收斂(下篇)

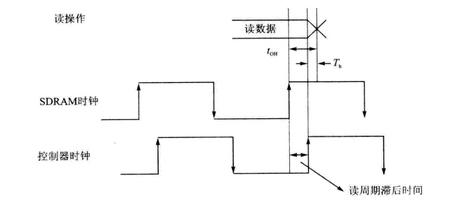

- 七、SDRAM工作時鐘相位偏移計算 從上篇文章中我們知道,我們的數(shù)據(jù)是要經過一定的延時才會到達目標器件的,這個延時也就是相對于源寄存器的時鐘發(fā)射沿的時間延時,數(shù)據(jù)在源寄存器時鐘的上升沿到來時輸出,經過FPGA的走線,PCB走線等,到達目標寄存器的數(shù)據(jù)端口時會有一定的延時,而這個數(shù)據(jù)要想被目標器件的目的寄存器鎖存,那么,目的寄存器的鎖存時鐘應該盡量在數(shù)據(jù)的有效窗口內才能確保數(shù)據(jù)被捕獲成功。所謂數(shù)據(jù)的有效窗口,就是數(shù)據(jù)在兩次變化之間的中間部分,也是數(shù)據(jù)最穩(wěn)定的部分。 所以,要想將數(shù)據(jù)正確捕獲,

- 關鍵字: FPGA SDRAM

英特爾的下一步:整合處理器核心與FPGA

- 自今年六月一號,英特爾宣布并購Altera后,雙方對于并購訊息就未再透露更多的訊息。不過,針對此點,Altera亞太區(qū)副總裁暨董事總經理莊秉翰引述英特爾所發(fā)布的公開訊息,也約略點出了英特爾并購Altera后的未來發(fā)展方向。 莊秉翰談到,眾所皆知,摩爾定律是由英特爾創(chuàng)辦人所創(chuàng),截至目前為止,英特爾仍然認為摩爾定律仍然適用于半導體產業(yè),同樣的,Altera也有相同的看法。 此外,英特爾也認為,并購Altera再整合自身旗下的IP等技術方案,可以創(chuàng)造出新一代的產品陣容,以滿足資料中心與物聯(lián)網(wǎng)的客戶群。

- 關鍵字: 英特爾 FPGA

fpga+mpu+mcu介紹

您好,目前還沒有人創(chuàng)建詞條fpga+mpu+mcu!

歡迎您創(chuàng)建該詞條,闡述對fpga+mpu+mcu的理解,并與今后在此搜索fpga+mpu+mcu的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga+mpu+mcu的理解,并與今后在此搜索fpga+mpu+mcu的朋友們分享。 創(chuàng)建詞條

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司