- Altera公司(NASDAQ: ALTR)日前宣布,推出40-Gbps以太網(40GbE)和100-Gbps以太網(100GbE)知識產權(IP)內核產品。這些內核能夠高效的構建需要大吞吐量標準以太網連接的系統,包括,芯片至光模塊、芯片至芯片以及背板應用等。

- 關鍵字:

Altera FPGA

- 系統級芯片(SoC)解決方案被譽為半導體業最重要的發展之一,目前,從數字手機和數字電視等消費類電子產品到高端通信LAN/WAN設備中,這一器件隨處可見。過去,為了創建此類嵌入式系統,設計工程師不得不在處理器、邏輯

- 關鍵字:

FPGA 方案 數字顯示 系統設計

- 在汽車電子中廣為采用的微控制器(MCU)正快速面臨時間和成本的壓力。使用MCU的主要優勢一直以來都是lsquo;創造具有高性價比的高階系統整合rsquo;。然而,在此一優勢之下,有一些與元件本身相關的潛在成本是超乎于其

- 關鍵字:

FPGA 車用 微控制器

- 為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設定不當帶來的數據不連續問題,結合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設定FIFO深度的方法。對FIFO不同深度的實驗表明,采用該方法設定的FIFO深度能夠

- 關鍵字:

LabVIEW FPGA FIFO 模塊

- 0 引言

傳統數字濾波器硬件的實現主要采用專用集成電路(ASIC)和數字信號處理器(DSP)來實現。FPGA內部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結構,這種結構特別適用于并行處理結構,相對于傳統方法來

- 關鍵字:

FPGA FIR 分布式算法 低通

- 摘要:為了產生穩定激勵信號的目的,采用Verilog硬件語言在FPGA上實現了數字頻率合成器的設計,該設計包括累加器、波形存儲器、AD轉換、低通濾波器等;對累加器、波形存儲器都進行了仿真,并下載到FPGA中,經A/D轉換

- 關鍵字:

FPGA 數字頻率合成器

- 摘要:高量程加速度傳感器在小信號的激勵下輸出在10 mV以內,傳統測試系統的噪聲可能覆蓋如此小的電壓信號,使高量程的加速度傳感器無法測試小的加速度信號。針對這一問題提出了基于自動增益切換控制理論的自適應數字

- 關鍵字:

FPGA 數字 傳感器設計

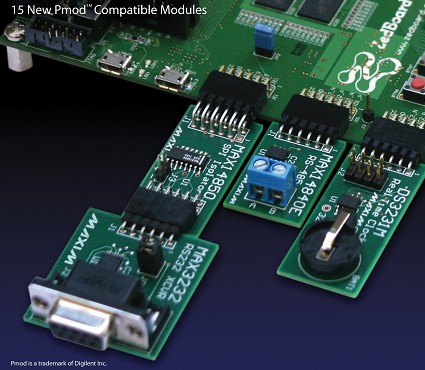

- Maxim Integrated Products (NASDAQ: MXIM)推出能夠直接插入符合Digilent? Pmod?標準的任意FPGA/CPU擴展端口的15個外設模塊套裝。簡單的連接操作和便利的軟件集成可加速原型開發進度,實現從概念至設計方案的快速移植。這套模塊的價格極具競爭力,即使在預算最緊張的情況下,也可以采用先進的高性能IC進行方案測試。

- 關鍵字:

Maxim FPGA

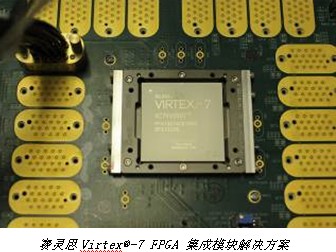

- All Programmable FPGA、SoC和3D IC的全球領先企業賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX) )宣布推出針對采用Virtex?-7 FPGA 集成模塊設計的全新解決方案, 該集成模塊可支持PCI Express (簡稱PCI-E) 3.0 x8標準和 DDR3 外部存儲器,能為開發人員提供立即啟動基于PCI-E 3.0的設計所需的全部構建模塊。

- 關鍵字:

賽靈思 FPGA Virtex-7

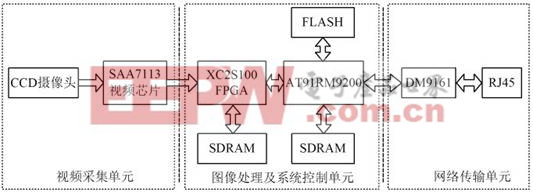

- 基于FPGA+嵌入式處理器的違章車輛視頻檢測系統,0 引 言隨著我國經濟的發展,機動車輛不斷地增長,現有道路等硬件設施的增長已經滿足不了日益膨脹的交通問題,智能交通系統(Intelligent Transportation System,ITS)越來越受重視。所謂智能交通系統(ITS)就是將先

- 關鍵字:

車輛 視頻 檢測系統 違章 處理器 FPGA 嵌入式 基于

- 0 引言目前,液晶顯示行業得到迅速的發展,但由于液晶模塊的生產不可能達到100%的成品率,或多或少地存在缺陷,目前在TFT模塊的生產工藝中就有可能產生點缺陷和線缺陷等。為了及早對產品的質量進行檢測,液晶測試儀器成為

- 關鍵字:

TFTLCD FPGA 信號源

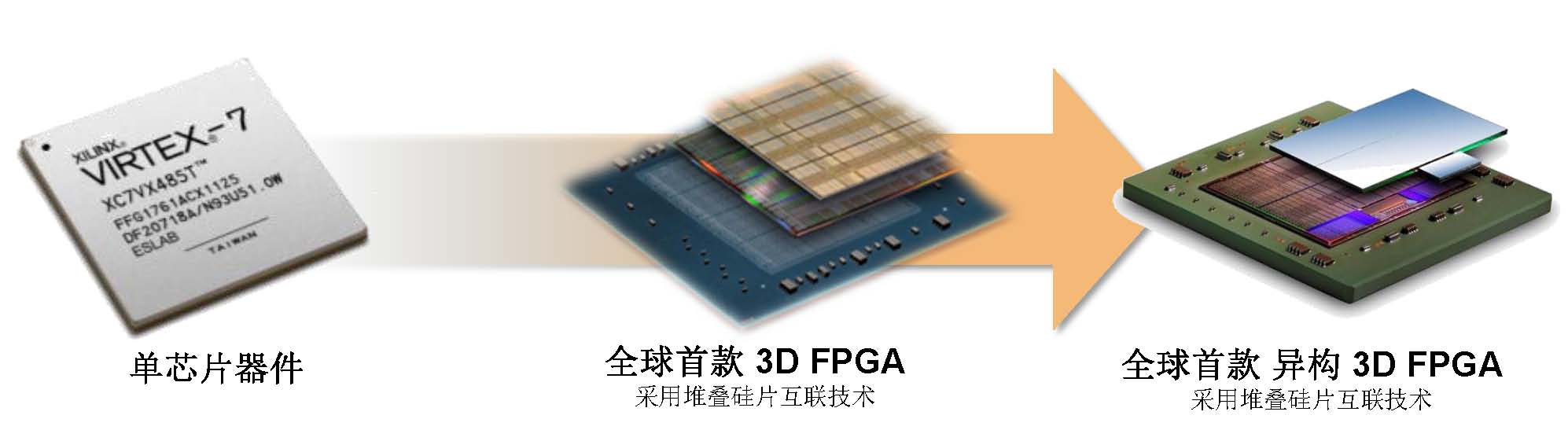

- 不久前,All Programmable技術和器件的企業——賽靈思公司(Xilinx)正式發貨 Virtex-7 H580T FPGA—全球首款3D異構All Programmable產品。

Virtex-7 HT采用賽靈思的堆疊硅片互聯 (SSI)技術,是提供業界帶寬最高的FPGA,可提供多達16個28 Gbps收發器和72個13.1 Gbps收發器,也是能滿足關鍵Nx100G和400G線路卡應用功能要求的單芯片解決方案。

為此,本刊訪問了該公司負責人,澄

- 關鍵字:

Xilinx 賽靈思 3D FPGA all programmable 異構

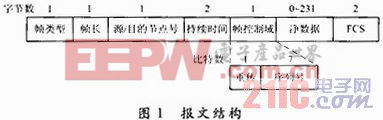

- 一種基于ARM和FPGA的可重構MAC協議設計,摘要:為了在實際信道條件下研究Ad Hoc網絡MAC協議,克服商業網卡芯片和理論仿真等帶來的局限性,搭建了基于ARM和FPGA相結合的硬件平臺,設計與實現了基于CSMA/CA的可重構MAC協議,并進行了仿真測試,驗證了該協議設

- 關鍵字:

協議 設計 MAC 重構 ARM FPGA 基于

- 傳統的綜合技術越來越不能滿足當今采用 90 納米及以下工藝節點實現的非常大且復雜的 FPGA 設計的需求了。問題是傳統的 FPGA 綜合引擎是基于源自 ASIC 的方法,如底層規劃、區域內優化 (IPO,In-place Optimization) 以

- 關鍵字:

Synplify Premier FPGA 時序收斂

fpga-ask介紹

您好,目前還沒有人創建詞條fpga-ask!

歡迎您創建該詞條,闡述對fpga-ask的理解,并與今后在此搜索fpga-ask的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473