- 摘要:針對某些特殊的測試試驗要求測試系統高性能、微體積、低功耗,在存儲測試理論基礎上,進行了動態存儲測試系統的FPGA設計。介紹了該系統的組成,對控制模塊進行了詳細設計。針對測試環境的多樣性設計了采樣策略

- 關鍵字:

FPGA 存儲測試 系統

- 摘要:介紹了一種基于Flash型FPGA的多路模擬重信號源設計方法,該系統以ACTEL公司的A3P125VQ100芯片為核心,實現了系統的軟硬件結合。它包括數模轉換單元、電源模塊、多路模擬開關模塊以及運算放大單元等,實現了電源

- 關鍵字:

Flash FPGA 信號源

- 摘要:為了在提高數據采集卡的速度的同時降低成本,設計了一種應用流水線存儲技術的數據采集系統。該系統應用軟件與硬件相結合的方式來控制實現,通過MAX1308模數轉換器完成ADC的轉化過程,采用多片Nandflash流水線

- 關鍵字:

FPGA 高速數據 采集 系統設計

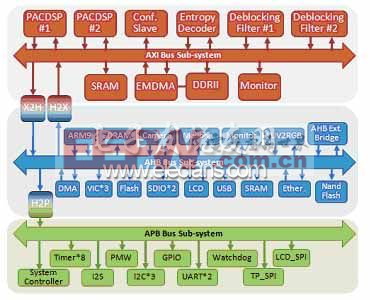

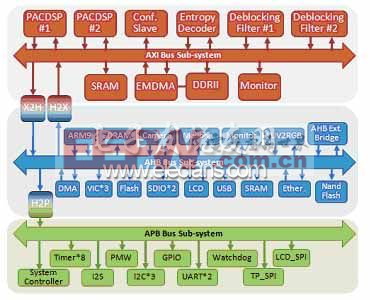

- 基于FPGA的SoC驗證平臺實現電路仿真偵錯,臺灣工業技術研究院提出一種能夠顯著提升客制化FPGA原型板驗證效率的創新方法,自動化現有的電路仿真(in-circuit emulation)偵錯功能,并提供更高的FPGA能見度。這個以FPGA為基礎的SoC驗證平臺對工研院而言是前景看好

- 關鍵字:

實現 電路 仿真 平臺 驗證 FPGA SoC 基于

- FPGA配置模式,FPGA有多種配置模式:并行主模式為一片FPGA加一片EPROM的方式;主從模式可以支持一片PROM編程多片FPGA;串行模式可以采用串行PROM編程FPGA;外設模式可以將FPGA作為微處理器的外設,由微處理器對其編程。 如何實現快

- 關鍵字:

模式 配置 FPGA

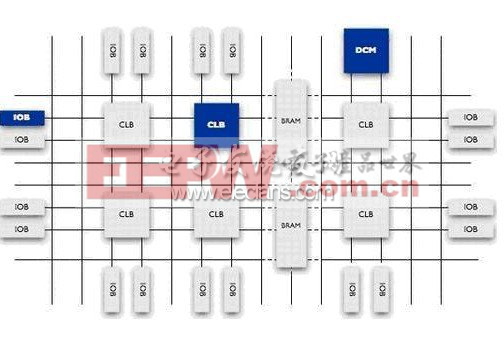

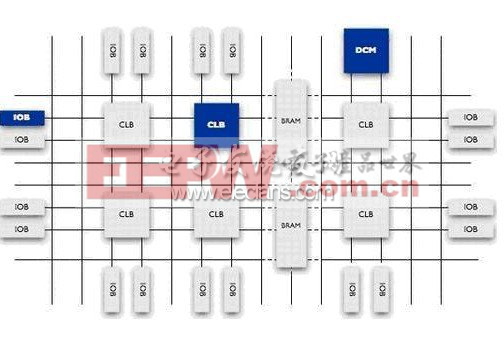

- FPGA芯片結構分析,目前主流的FPGA仍是基于查找表技術的,已經遠遠超出了先前版本的基本性能,并且整合了常用功能(如RAM、時鐘管理和DSP)的硬核(ASIC型)模塊。如圖1-1所示(注:圖1-1只是一個示意圖,實際上每一個系列的FPGA都有其相應的

- 關鍵字:

分析 結構 芯片 FPGA

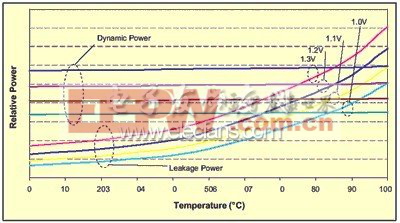

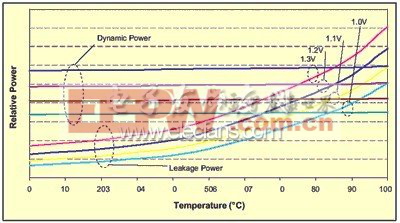

- 現代FPGA設計的能源優化方案,引言 減少FPGA的功耗可帶來許多好處,如提高可靠性、降低冷卻成本、簡化電源和供電方式、延長便攜系統的電池壽命等。無損于性能的低功耗設計 既需要有高功率效率的FPGA架構,也需要有能駕馭架構組件的良好設計規范

- 關鍵字:

優化 方案 能源 設計 FPGA 現代

- TMS320C61416控制FPGA數據加載設計,本文提出了采用通過市面上常見的Flash ROM芯片替代專用PROM的方式,通過DSP的外部高速總線進行FPGA加載;既節約了系統成本,也能達到FPGA上電迅速加載的目的;特別適用于在FPGA調試后期,待固化程序的階段。下面以兩片Xilinx公司Virtex-4系列XC4VLX60芯片為例,詳細介紹采用TI公司的TMS320C61416 DSP控制FPGA芯片數據加載的軟硬件設計。

- 關鍵字:

加載 設計 數據 FPGA 控制 TMS320C61416

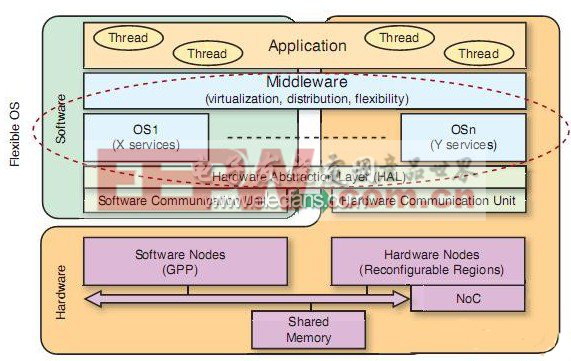

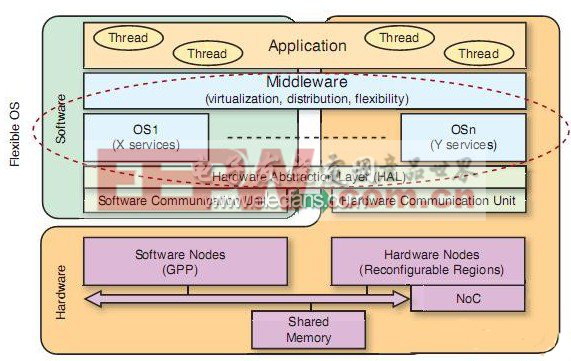

- 可擴展動態重配置的新型FPGA平臺設計,新型 FPGA 平臺具有高度的靈活性和可擴展性,且集成度高,能夠在單個或兩個芯片上集成一個完整的異構動態運算系統。 自適應硬件在諸如導彈電子和軟件無線電等功耗和系統尺寸有限,同時對環境高度敏感的應用中非常

- 關鍵字:

平臺 設計 FPGA 新型 動態 配置 擴展

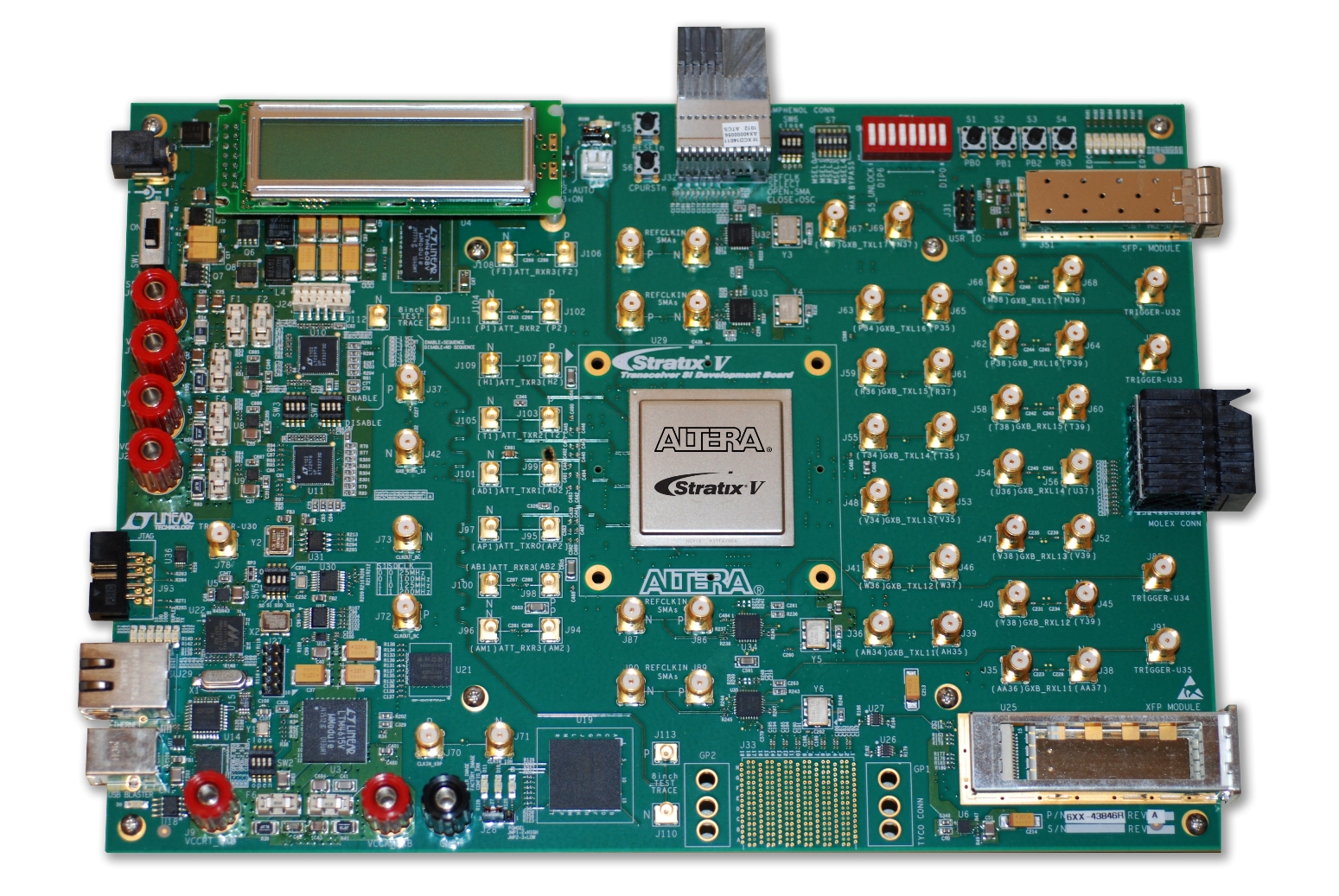

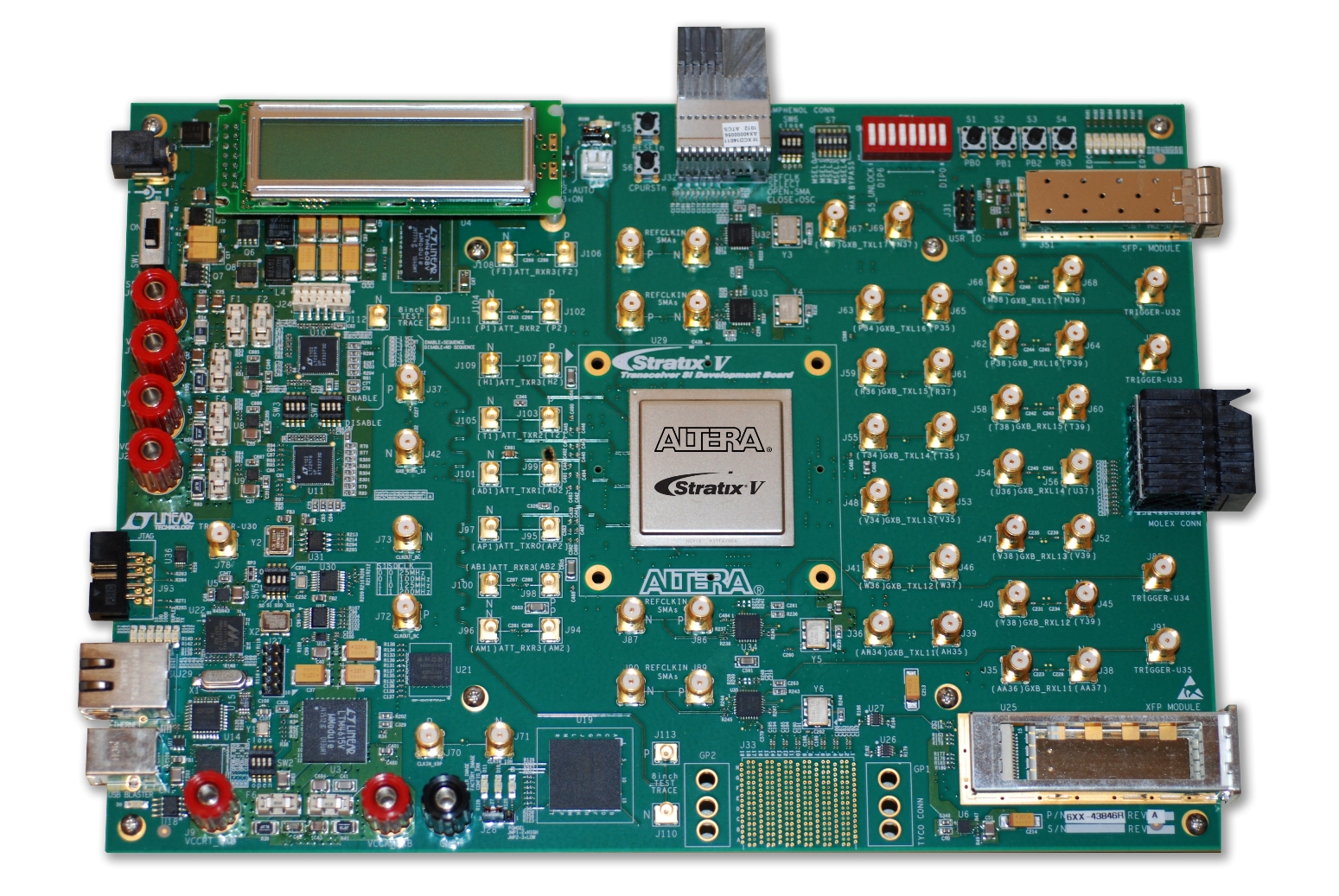

- Altera公司日前宣布開始提供第一款帶有28-nm FPGA的開發套件——Stratix V GX FPGA信號完整性套件,在推動業界28-nm FPGA發展方面樹立了新里程碑。這一全功能套件支持設計工程師加速高性能系統的設計和開發,滿足了業界對提高帶寬的需求。Stratix V GX FPGA信號完整性開發套件為用戶提供的平臺能夠測量并評估從600 Mbps到12.5 Gbps的收發器鏈路性能。

- 關鍵字:

Altera FPGA

- 基于FPGA的TMR方法改進策略,基于SRAM的FPGA對于空間粒子輻射非常敏感,很容易產生軟故障,所以對基于FPGA的電子系統采取容錯措施以防止此類故障的出現是非常重要的。三模冗余(TMR)方法以其實現的簡單性和效果的可靠性而被廣泛用于對單粒子翻轉(

- 關鍵字:

改進 策略 方法 TMR FPGA 基于

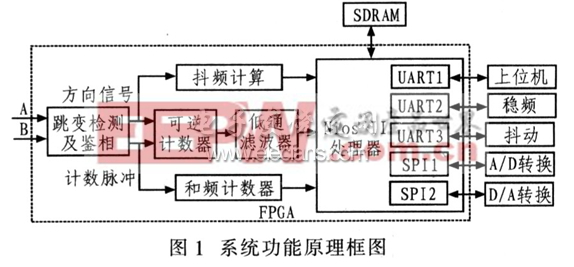

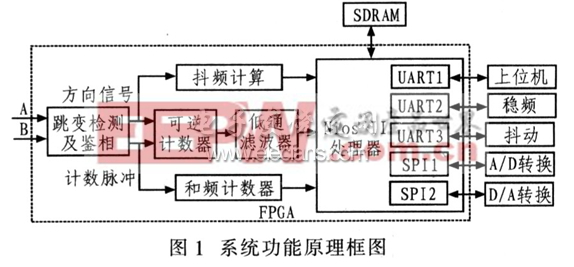

- Nios II實現二頻機抖陀螺工作電路設計,激光陀螺的工作原理是Sagnac效應,與傳統的機械陀螺相比,激光陀螺具有精度高、耐環境性能好、動態性能好、啟動時間短、壽命長及數字式輸出等特點,是捷聯式慣性導航系統的理想元件。 二頻機抖陀螺工作電路包括高

- 關鍵字:

工作 電路設計 陀螺 實現 II Nios

- 2011年9月7號,北京——Altera公司(NASDAQ:ALTR)今天宣布開始提供第一款帶有28-nm FPGA的開發套件——Stratix V GX FPGA信號完整性套件,在推動業界28-nm FPGA發展方面樹立了新里程碑。這一全功能套件支持設計工程師加速高性能系統的設計和開發,滿足了業界對提高帶寬的需求。Stratix V GX FPGA信號完整性開發套件為用戶提供的平臺能夠測量并評估從600 Mbps到12.5 Gbps的收發器鏈路性能。

- 關鍵字:

Altera FPGA Stratix V GX

- 基于NiosⅡ的電能質量監測系統設計,在電力系統的電能質量參數檢測中,利用可編程邏輯器件的可在線編程特點和SoPC的技術優勢,在FPGA中嵌入了32位NiosⅡ軟核系統,探討了處理諧波數據的FFT算法和硬件系統結構的設計,可實現對電能信號的采集、處理、存儲

- 關鍵字:

系統 設計 監測 質量 Nios 電能 基于

- 致力于提供幫助功率管理、安全、可靠與高性能半導體技術產品的領先供應商美高森美公司(Microsemi Corporation,紐約納斯達克交易所代號:MSCC) 宣布提供經成本優化的SmartFusion 可定制單芯片系統 (customizable system-on-chip, cSoC) 器件A2F060,該器件備有商用和工業溫度等級型款,專門針對大批量應用而設計,包括馬達和運動控制、游戲機、太陽能逆變器,以及臨床和成像醫療電子設備。

- 關鍵字:

美高森美 FPGA

fpga-nios介紹

您好,目前還沒有人創建詞條fpga-nios!

歡迎您創建該詞條,闡述對fpga-nios的理解,并與今后在此搜索fpga-nios的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473