- 中國上海,2009年3月31日——ARM公司(倫敦證交所:ARM;納斯達克:ARMH)近日在于美國加州圣何塞舉行的嵌入式系統大會(ESC)上發布了Keil™ 微控制器樣機系統(MPS: Microcontroller Prototyping System),能夠對單一產品中的ARM® Cortex™-M系列處理器以及用戶定義的外設進行評估和樣機建立。Keil MPS是首個包含了全速的、FPGA形式的Cortex-M0或Cortex-M3處理器的樣

- 關鍵字:

ARM FPGA 處理器

- 分析了與標準805l MCU兼容的MC805l IP核結構原理與設計層次,詳細論述了MC8051 IP核的FPGA實現與應用方法。通過試驗驗證,其性能比標準8051 MCU高,方便與系統其他模塊的集成。在各種嵌入式系統和片上系統中使用該IP核具有重要意義。

- 關鍵字:

8051 FPGA MC IP核

- 2009年3月31號,北京——Altera公司(NASDAQ: ALTR)今天宣布,Altera公司于2009年3月10日在天津大學成立EDA/SOPC聯合實驗室。這是Altera自2004年3月在中國電子科技大學成立首個EDA/SOPC聯合實驗室以來的國內第60所聯合實驗室和培訓中心。該實驗室將為數字邏輯電路、硬件描述語言、微機原理、電視原理、現代數字系統設計等本科或研究生課程的實驗教學以及電子類課程設計提供支持,Altera®公司的FPGA開發環境將成為貫穿天津大學

- 關鍵字:

Altera FPGA SOPC

- 0 引言

信息技術的發展,特別是各種數字處理器件處理速度的提高,實時處理大量的數據已經成為現實。但是,在一些惡劣環境和數據無法進行實時傳輸的情況下,還必須用到存儲測試的方法。存儲測試是指在對被測對象

- 關鍵字:

FPGA 高速數據 采集 存儲系統

- O 引言

現場可編程門陣列(FPGA,Field Programmable Gate Array)的出現是超大規模集成電路(VISI)技術和計算機輔助設計(CAD)技術發展的結果。FPGA器件集成度高、體積小,具有通過用戶編程實現專門應用的的功能。

- 關鍵字:

144C T144 FPGA 144

- 1 Fir濾波器原理

有限沖激響應(FIR)數字濾波器和無限沖激響應(IIR)數字濾波器廣泛應用于數字信號處理系統中。IIR數字濾波器方便簡單,但它相位的非線性,要求采用全通網絡進行相位校正,且穩定性難以保障。FIR濾

- 關鍵字:

FPGA FIR 并行 流水線

- 摘要:基于FIR數字濾波器的原理和層次化、模塊化設計思想,結合Altera公司的CycloneII系列FPGA芯片,提出了FIR數字濾波器的實現硬件方案,給出了采用Matlab、QuartusⅡ設計及實現32階低通FIR濾波器的方法步驟,仿真及

- 關鍵字:

Matlab FPGA FIR 數字

- Altera公司今天宣布,Altera公司于2009年3月10日在天津大學成立EDA/SOPC聯合實驗室。這是Altera自2004年3月在中國電子科技大學成立首個EDA/SOPC聯合實驗室以來的國內第60所聯合實驗室和培訓中心。該實驗室將為數字邏輯電路、硬件描述語言、微機原理、電視原理、現代數字系統設計等本科或研究生課程的實驗教學以及電子類課程設計提供支持,Altera®公司的FPGA開發環境將成為貫穿天津大學電子工程類專業本科和研究生教育階段的實驗平臺。

作為全球領先的可編程邏輯器件

- 關鍵字:

Altera FPGA SOPC

- 在高速圖像采集系統中,CPU時鐘資源、I/O端口資源、傳輸單元等都成為系統的瓶頸。本系統采用FPGA+RAM+USB的設計:FPGA硬件采樣模塊,有效降低采樣時延和CPU時鐘資源;獨特的RAM時序控制與讀寫控制分離設計,增加了模塊之間的獨立性,降低了控制的復雜度;USB設計在實現高速率數據傳輸的同時又具有低成本、易安裝等優點。

- 關鍵字:

FPGA 高速圖像采集 系統設計

- 實現信號源常用的方法是頻率合成法,其中直接數字頻率合成法是繼直接頻率合成法和間接頻率合成法之后,隨著電子技術迅速發展的第三代頻率合成技術。DDS是一種全數字技術,它從相位概念出發直接合成所需頻率,它具有頻

- 關鍵字:

Builder FPGA DSP 正弦

- 隨著芯片制造技術的發展,SOPC(可編程單芯片系統)已成為嵌入式系統設計的一個發展方向。Altera公司推出的NIOS II嵌入式處理器系統,是目前比較流行的SOPC。它通常由NIOS II處理器、Avalon總線結構和各種外圍設備(

- 關鍵字:

NIOS II 嵌入式 處理器系統

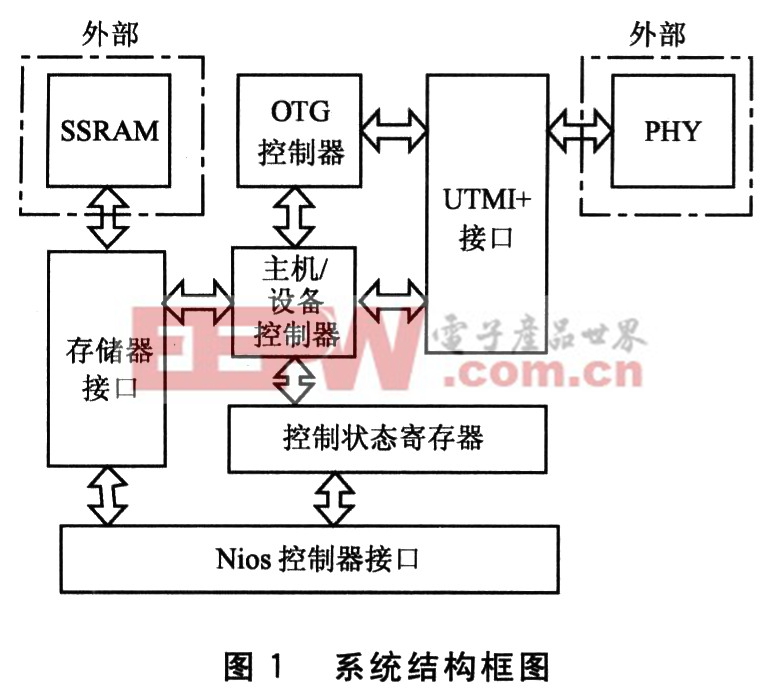

- 為了實現USB設備之間的直接通信,介紹一款USB 0TG IP核的設計與FPGA驗證。在分析OTG補充規范的基礎上,重點描述了USB OTG IP核的設計原理、模塊劃分以及每個模塊的功能,然后對USBOTG的部分特性進行詳細的闡述,最后給出該IP核在ModelSim中的功能仿真及FPGA驗證結果。結果表明,該IP核具備主機功能和設備功能,可作為一個獨立的IP模塊應用到SoC系統中。

- 關鍵字:

FPGA 驗證 設計 Core OTG IP USB

- 0 引言 短波信道存在多徑時延、多普勒頻移和擴散、高斯白噪聲干擾等復雜現象。為了測試短波通信設備的性能,通常需要進行大量的外場實驗。相比之下,信道模擬器能夠在實驗室環境下進行類似的性能測試,而且測試費用

- 關鍵字:

FPGA 高斯白噪聲 方法 序列

fpga-nios介紹

您好,目前還沒有人創建詞條fpga-nios!

歡迎您創建該詞條,闡述對fpga-nios的理解,并與今后在此搜索fpga-nios的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473