- 球可編程平臺領導廠商賽靈思公司與Vanguard Software Solutions 公司 (VSofts) 在 IBC2010 大會上聯合演示了 VSofts H.264/AVC-I IP 核的強大功能:能實現超低延時,且其現場可編程門陣列 (FPGA) 實施方案不僅符合國際電信聯盟 (ITU) 和 Panasonic AVC-Intra 標準,而且還支持業界標準的編解碼器,能在實時視頻廣播應用中確保源視頻到編碼視頻的最小延遲。

VSofts 市場營銷副總裁 Felix Nemirovsky

- 關鍵字:

賽靈思 FPGA IP核

- 美國國家儀器有限公司(National Instruments,簡稱NI)近日發布NI 9157和NI 9159 MXI-Express RIO機箱,以及NI 9148以太網RIO機箱,這三款新產品在現有的NI 9144 EtherCAT機箱基礎上,進一步擴展了NI基于各種總線的高通道數擴展機箱系列產品。利用NI可重配置I/O(RIO)技術,這些機箱將基于現場可編程門陣列(FPGA)的硬件和C系列I/O應用到了需要數百甚至數千通道數的應用。每一個擴展機箱含有一個可用NI LabVIEW FPGA模塊編

- 關鍵字:

NI FPGA LabVIEW

- 針對DDS頻率轉換時間短,分辨率高等優點,提出了基于FPGA芯片設計DDS系統的方案。該方案利用A1tera公司的QuartusⅡ開發軟件,完成DDS核心部分即相位累加器和ROM查找表的設計,可得到相位連續、頻率可變的信號,并通過單片機配置FPGA的E2PROM完成對DDS硬件的下載,最后完成每個模塊與系統的時序仿真。經過電路設計和模塊仿真,驗證了設計的正確性。由于FPGA的可編程性,使得修改和優化DDS的功能非常快捷。

- 關鍵字:

FPGA DDS

- 愛特公司(Actel CorporaTIon) 宣布其多種FPGA產品現可搭配使用加密內核,對抗差分功率分析(differential Power analysis, DPA)攻擊。采用SmartFusion、Fusion、ProASIC3和 IGLOO的設計人員現可通過使用IP Cores公司(IP Cores, Inc.)的AES、GCM或ECC IP內核,保護其密鑰不受DPA攻擊。IP Cores是專業提供主要用于安全和加密領域的半導體用IP內核的供應商,而這些內核則是首次商業化地用于FPGA的

- 關鍵字:

Actel FPGA

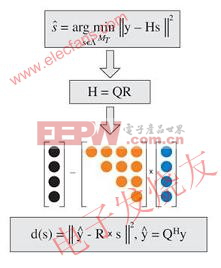

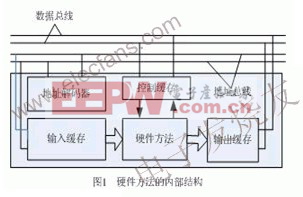

- 空分復用 (SDM) MIMO 處理可顯著提高頻譜效率,進而大幅增加無線通信系統的容量。空分復用 MIMO 通信系統作為一種能夠大幅提升無線系統容量和連接可靠性的手段,近來吸引了人們的廣泛關注。 MIMO 無線系統最

- 關鍵字:

系統 應用 FPGA 實現 通信 MIMO 檢測 空分 復用 球形

- 基于Java的FPGA可編程嵌入式系統, 傳統的嵌入式產品只能實現某種特定的功能,不能滿足用戶可變的豐富多彩的應用需求。為解決這個問題,本文設計并實現了一種使用Java作為軟件平臺的基于FPGA的可編程嵌入式系統,以實現系統對多種本地應用和網絡的

- 關鍵字:

嵌入式 系統 可編程 FPGA Java 基于

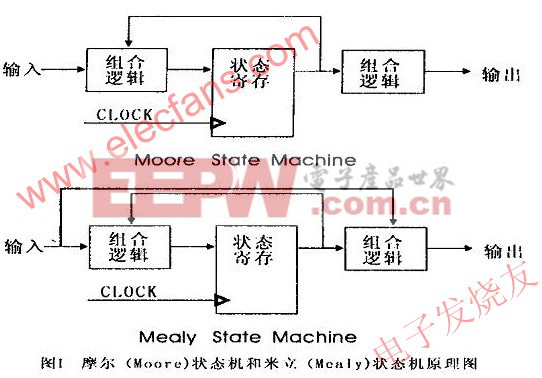

- FPGA/CPLD狀態機的穩定性設計, 隨著大規模和超大規模FPGA/CPLD器件的誕生和發展,以HDL(硬件描述語言)為工具、FPGA/CPLD器件為載體的EDA技術的應用越來越廣泛.從小型電子系統到大規模SOC(Systemonachip)設計,已經無處不在.在FPGA/CPLD設計中,狀

- 關鍵字:

設計 穩定性 狀態 FPGA/CPLD

- FPGA全局時鐘資源相關原語及使用, FPGA全局時鐘資源一般使用全銅層工藝實現,并設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達芯片內部的所有可配置單元(CLB)、I/O單元(IOB)和選擇性塊RAM(Block Select RAM)的時延和抖動都為最小。為了適應復雜

- 關鍵字:

相關 使用 資源 時鐘 全局 FPGA

- MathWorks面向使用MATLAB和Simulink設計高級信號處理和通信系統發布了重要的新功能。憑借常規的射頻子系統建模、高級電路包絡和諧波平衡分析方法,新的 SimRF 產品使系統架構師可以使用 Simulink 來設計和驗證完整的無線通信系統。對Simulink HDL Coder 進行的一些重要更新,為自動 HDL 代碼生成添加了關鍵路徑分析和面積-速度優化功能,以及輔助實現 FPGA 全新的 Workflow Advisor。Communications Blockset、Signal

- 關鍵字:

Simulink 高級信號處理 FPGA

- 美國國家儀器有限公司(National Instruments,簡稱NI)近日發布NI 9157和NI 9159 MXI-Express RIO機箱,以及NI 9148以太網RIO機箱,這三款新產品在現有的NI 9144 EtherCAT機箱基礎上,進一步擴展了NI基于各種總線的高通道數擴展機箱系列產品。利用NI可重配置I/O(RIO)技術,這些機箱將基于現場可編程門陣列(FPGA)的硬件和C系列I/O應用到了需要數百甚至數千通道數的應用。每一個擴展機箱含有一個可用NI LabVIEW FPGA模塊編

- 關鍵字:

NI LabVIEW FPGA

- 現代電子戰環境復雜,信號密度大,所以對信號的實時分選很重要。這里,提出一種基于關聯比較器的雷達信號分選方法,在實現多參數分選的同時,也保證了實時性。詳細闡述了在Virtex 4系列FPGA上實現基于內容可尋存儲器(CAM)的關聯比較器的途徑。

- 關鍵字:

FPGA 雷達 脈沖 預分選器

- 在從圖像源到終端顯示的過程中,電路噪聲、傳輸損耗等會造成圖像質量下降,為了改善顯示器的視覺效果,常常需...

- 關鍵字:

FPGA 圖像增強 視頻圖像處理

- 顧名思義,嵌入式系統指的是嵌入到系統內部的計算機系統,是面向特定應用設計的專用計算機系統。 早期的嵌入式系統一般是以通用處理器或單片機為核心,在外圍電路中加入存儲器、功率驅動器、通信接口、顯示接口

- 關鍵字:

FPGA 嵌入式系統 發展 方向

fpga-to-asic介紹

您好,目前還沒有人創建詞條fpga-to-asic!

歡迎您創建該詞條,闡述對fpga-to-asic的理解,并與今后在此搜索fpga-to-asic的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473