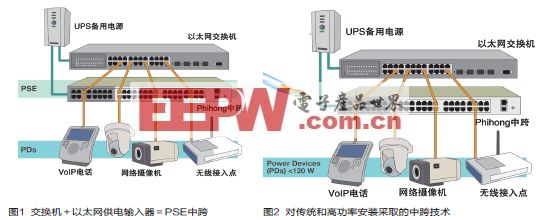

- 以太網供電技術(Power over Ethernet ,PoE)的采用一直以來受到以太網交換機對網絡輸送電力和數據容量的限制,但是一個新的概念,中間跨接法(Mid-span),可以在不購買新交換機的情況下,為網絡增添以太網供電容量。

- 關鍵字:

PoE 以太網 201012

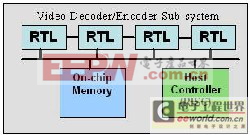

- 利用可配置處理器來創建多標準多分辨率視頻引擎, 隨著消費類電子產品,尤其是手機、PDA和便攜式媒體播放器(PMP)的急劇發展,其對于終端硅供應商的要求也大大提高。對這些供應商來說,設計僅僅能夠適用于一到兩個多媒體編解碼器或無線標準的IC已經遠遠不夠了。消

- 關鍵字:

分辨率 視頻 引擎 標準 創建 配置 處理器 利用

- 本設計采用MSP430F147單片機和以太網供電管理器TPS23841、TPS2376H開發了兼容IEEE802.3af標準的高功率PoE系統。此系統也可應用在醫療、工業等21.5~57V、最高功率為25 W的供電環境中,具有良好的兼容性。

- 關鍵字:

系統 設計 PoE 功率 標準 兼容

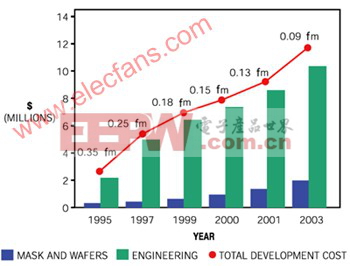

- 標準單元ASIC和FPGA的權衡及結構化ASIC,多種制造FPGA的深亞微米工藝,如Xilinx公司最新Spartan-3系列產品采用的90納米工藝(參考文獻1),使每塊芯片上的門電路數量變得越來越大。如果您的設計使用FPGA的嵌入式存儲器陣列和擴散式模擬及數字功能模塊,如DL

- 關鍵字:

ASIC 結構化 權衡 FPGA 標準 單元

- 人們都傾向于按照基本的60Hz或50Hz頻率考慮電力線上的能量——這也是電站的渦輪和發電機產生電壓的方式。當然,如果有無功負載,電流就會滯后于電壓。這就是“功率因數”,對嗎?但難道它仍然

- 關鍵字:

優化 解決方案 標準 校正 因數 功率

- 針對以太網電源(PoE)的IEEE 802.3af標準規定將直流電源與10/100/1000 Mbps數據一起傳輸,從而為以太網帶來了新的面貌。其中,PoE帶來了一系列獨特的問題,對于許多具備設計以太網設備經驗的工程師來說,他們并不熟

- 關鍵字:

功率 設計 PoE 電源 以太網 針對

- 美國能源部(DOE)的JamesA.Barnes博士在EVS25先進電池技術研討會上表示,2010年,美國能源部在動力電池及材料...

- 關鍵字:

電池技術 標準

- 基于FMC標準的FPGA夾層卡I/O設計, 面對似乎層出不窮的新 I/O 標準,目前嵌入式系統設計人員繼續依靠 FPGA 來部署系統日益重要的外部 I/O 接口,這點絲毫不足為奇。FPGA 可提供大量可配置的 I/O,能在適當 IP 基礎上支持幾乎無限多種高度復雜的 I/O

- 關鍵字:

I/O 設計 夾層 FPGA FMC 標準 基于

- 引言 本文介紹了如何通過MAX2990電力線通信調制解調器的I2C接口與外部EEPROM 24C04連接,并給出了相應的固件例程。Isup2;C總線受控于MAX2990 (主機),24C04 EEPROM為從機器件。以下框圖給出了本文示例的硬件

- 關鍵字:

EEPROM 24C04 連接 標準 接口 通過 MAX2990 I2C 如何

- 圖中所示由SW399組成的標準電池替換器.圖示線路是可代替標準電池使用的輸出電壓1.01V的,極穩定的電壓標準用電源.微調電位器雖然可作溫度漂移調整用和輸出電壓微調用,但如果不采用溫度系數小的就會影響性能.

- 關鍵字:

替換 電路圖 電池 標準 組成 SW399

- 摘要 IP/MPLS網絡運營商如果采用L2VPN技術,就可以利用IP/MPLS網絡同時支持IP業務和數據業務,提高網絡資源的使用和管理效率,這項技術因此得到了運營商的關注。本文概要介紹了L2VPN技術的三種實現方式,并介紹國內

- 關鍵字:

實現 標準 技術 L2VPN 虛擬 專用網 二層

- 計算機機房照明的好壞不僅會影響計算機操作人員和軟、硬件維修人員的工作效率和身心健康,而且還會影響到電子機房的可靠運行。因此合理的選擇照明控制方式、燈具類型、布局及一些相關器材等在電子機房的裝修和電

- 關鍵字:

設計 方案 標準 照明 機房 計算機

- 目前手機的發展已成了全球電子業共同的焦點所在,除了語音與照相功能外,手機下一步的目標顯然是要將視頻多媒體的娛樂功能也納入其中。這是一個相當具有突破性的概念和技術挑戰,未來的手機將不只是電話、相機或

- 關鍵字:

挑戰 標準 手機 電視

- 計算機機房照明的好壞不僅會影響計算機操作人員和軟、硬件維修人員的工作效率和身心健康,而且還會影響到電子機房的可靠運行。因此合理的選擇照明控制方式、燈具類型、布局及一些相關器材等在電子機房的裝修和電氣

- 關鍵字:

機房照明 標準 照度 設計方法

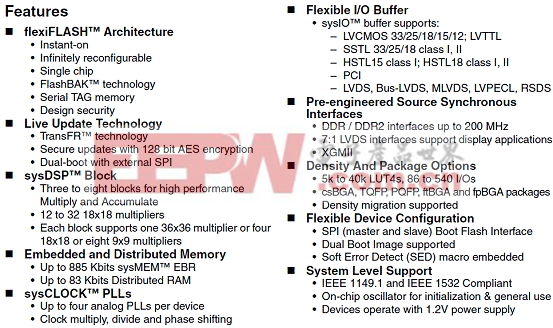

- 基于LatticeXP2設計的FPGA標準評估技術,LatticeXP2器件包括基于查找表(LUT)的 FPGA以及非易失閃存單元(flexiFLASH)。LatticeXP2系列器件的LUT從5K到40K,分布是RAM從10K到83Kb,EBR SRAM從166Kb到885Kb,EBR SRAM區塊從9到48個,sysDSP從3個到8個,18x

- 關鍵字:

評估 技術 標準 FPGA LatticeXP2 設計 基于

poe+標準介紹

您好,目前還沒有人創建詞條poe+標準!

歡迎您創建該詞條,闡述對poe+標準的理解,并與今后在此搜索poe+標準的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473