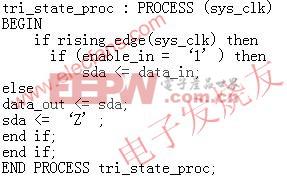

- 基于VHDL和FPGA的多種分頻的實現方法,分頻器是數字系統設計中的基本電路,根據不同設計的需要,我們會遇到偶數分頻、奇數分頻、半整數分頻等,有時要求等占空比,有時要求非等占空比。在同一個設計中有時要求多種形式的分頻。通常由計數器或計數器的級聯

- 關鍵字:

實現 方法 多種 FPGA VHDL 基于

- 摘 要:為了有效防止機械式鍵盤按鍵抖動帶來的數據錯誤,這里在Quartus Ⅱ開發環境下,采用VHDL 語言設計了一種能夠將機械式4 times;4 矩陣鍵盤的按鍵值依次顯示到8 個7 段數碼管上的矩陣鍵盤及顯示電路。仿真結果表

- 關鍵字:

FPGA/ CPLD 鍵盤 電路

- 全球可編程邏輯解決方案領導廠商賽靈思公司,2010年9月14日宣布與四川虹視顯示技術有限公司(簡稱四川虹視)在成都高新區共同成立FPGA聯合實驗室, 致力于推動虹視公司最新的OLED產品技術研發,賽靈思全球消費市場總監Harry Raftopoulos,高級技術市場經理酆毅,四川虹視總經理郎豐偉,技術總監文東星、產品研發中心部長田朝勇等出席了簽字揭牌儀式。

根據雙方當天簽署的協議,賽靈思公司計劃向四川虹視提供技術培訓,以及多套開發工具,如Spartan®-6 消費視頻開發套件,Spart

- 關鍵字:

賽靈思 FPGA

- TSMC 5日宣布,硅知識產權聯盟的結盟范圍將擴大至Soft IP業者,未來將有完備的Soft IP供先進技術使用,進而加速客戶產品的上市時程。

經由此一Soft IP結盟方案,TSMC將提供特定的設計文件與技術資訊,讓技術伙伴得以充分地將Soft IP在TSMC的技術基礎上予以最佳化。同時,TSMC也與這些公司合作,使其soft IP的發展與公司的工藝技術發展時程達到一致,以加速他們soft IP準備就緒的時程。

一直以來,Soft IP的發展獨立于工藝技術之外已行之有年,也因此Soft

- 關鍵字:

IP SoC

- FPGA全局時鐘資源一般使用全銅層工藝實現,并設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達芯片內部的...

- 關鍵字:

FPGA 全局時鐘 BUFG

- 提出了一種基于FPGA的雙通道旋轉變壓器測角電路設計方案,通過FPGA來控制AD2S82A、AD2S80A的解碼和同步問題。同時用FPGA對轉換后數據進行誤差補償和組合,以及二進制角度值的轉換,提高了整個系統的集成度和可靠度。整個電路在Altium Designer 9.O設計環境下設計實現。采用Altera公司的EP2C35F484C6型FPGA芯片進行FPGA部分的仿真,實驗和仿真的結果很好地實現了該方案的設計功能,并滿足高精度、高速度轉換的設計要求。

- 關鍵字:

FPGA 雙通道 測角系統 旋轉變壓器

- 基于FPGA的協方差矩陣運算的實現大多采用的是定點計算方式,在運算過程中,存在數據處理動態范圍小,容易溢出,截斷誤差等問題。加之以空間譜估計為研究背景的協方差矩陣運算,大多得到的是針對特殊陣列模型的實對稱矩陣,不具備通用性。針對定點運算的不足和該運算的適用范圍,研究了浮點運算和復數運算的特點,提出了基于復數矢量的浮點協方差運算的FPGA實現方案。在Altera\stratix\EP1S20F780C7中的仿真和調試結果表明了該方案的有效性。

- 關鍵字:

FPGA 浮點 協方差矩陣

- 針對數字基帶信號的特點和通信系統中對數字信號傳輸的要求,研究一種基于FPGA的DSP技術和DDS技術的軟件無線電調制器的設計方法。在FPGA平臺上設計具有ASK,FSK,PSK和QAM調制功能的軟件無線電調制器。該系統具有可重復編程和動態重構的優點,使系統易于修改和功能升級,靈活性強。

- 關鍵字:

FPGA 軟件無線電 制器設計

- FPGA時序收斂,您編寫的代碼是不是雖然在仿真器中表現正常,但是在現場卻斷斷續續出錯?要不然就是有可能在您使用更高版本的工具鏈進行編譯時,它開始出錯。您檢查自己的測試平臺,并確認測試已經做到 100% 的完全覆蓋,而且所有測試

- 關鍵字:

收斂 時序 FPGA

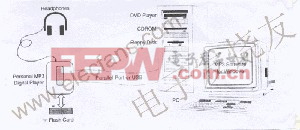

- MP3數字播放機系統的FPGA設計,1 引 言

MPEG(活動影像專業人員組織)是為數字音頻確定單一編碼和解碼(壓縮/解壓縮)方法于1988年建立的。1992年,國際標準組織(ISO)和國際電工委員會(IEC)為音頻和視頻編碼建立了MPEG1(ISO/IEC11172)標準

- 關鍵字:

FPGA 設計 系統 播放機 數字 MP3

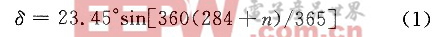

- 基于 FPGA XC3S1500開發板的太陽能自動跟蹤系統, 本設計采用傳統的視日運動跟蹤法,利用Xilinx公司提供的FPGA開發環境ISE,設計完成了基于XC3S1500開發板的太陽能自動跟蹤系統,以實現對太陽的全天候、全自動、實時精確控制。 1 視日運動跟蹤法 視日運動跟

- 關鍵字:

自動 跟蹤 系統 太陽能 開發 FPGA XC3S1500 基于

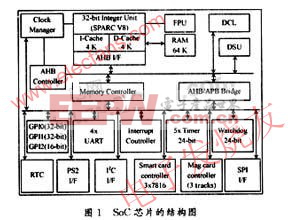

- 電子記帳控稅終端機設計的片上系統SOC芯片研究,1 引 言

電子記帳控稅終端機屬于高度安全和可靠的產品,關系到信息安全和金融安全,長期使用國外的核心器件將給國家安全帶來嚴重隱患。擁有自主知識產權的嵌入式處理器、專用芯片及其嵌入式操作系統已成為振興我國

- 關鍵字:

SOC 芯片 研究 系統 設計 記帳 終端機 電子

- 基于FPGA的多模無線基站,FPGA 類高性能可編程邏輯器件,正是多模無線基站的最佳構建平臺之一。Xilinx率先發布和量產的65nm平臺FPGA,則以大量先進技術和全新的設計有效增加了系統產品的生命周期并滿足了3G、LTE、IMT-Advanced等移動通信標準

- 關鍵字:

基站 無線 多模 FPGA 基于

- 提出一種基于DDS和FPGA技術的高動態擴頻仿真信號源的實現方案。采用了DDS技術的芯片AD9854和AD9850,能夠模擬多普勒頻移,實現高動態環境仿真。載波中心頻率變化范圍達到100kHz,變化率1.8kHz/s。

- 關鍵字:

FPGA DDS 動態 擴頻

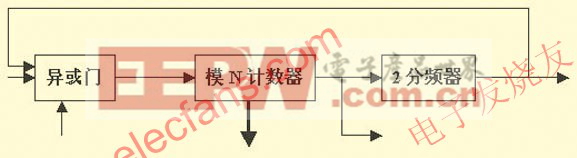

- 一般的位同步電路大多采用標準邏輯器件按傳統數字系統設計方法構成,具有功耗大,可靠性低的缺點。用FPGA設計電路具有很高的靈活性和可靠性,可以提高集成度和設計速度,增強系統的整體性能。本文給出了一種基于fpga的數字鎖相環位同步提取電路。

- 關鍵字:

FPGA 鎖相環 電路設計 位同步

soc-fpga介紹

您好,目前還沒有人創建詞條soc-fpga!

歡迎您創建該詞條,闡述對soc-fpga的理解,并與今后在此搜索soc-fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473