某定向設備采用多普勒效應測向原理,即當天線振子做圓周運動時,天線振子本身與目標信號源就會產生相對速度,使振子感應到的信號產生了多普勒頻移,通過對振子感應信號相位的處理,從而達到測向的目的。而為了提高天

關鍵字:

FPGA VHDL 選通電路 分頻

上周我跟我同事說,“ 兩種語言阻礙了嵌入式系統開發人員和軟件工程師借助Zynq SOCs來提升系統性能。”那就是“Verilog” 和 “VHDL”正如期待那樣,這已經得到了解決—因為SD

關鍵字:

Verilog VHDL SDSoC

隨著科學研究與技術開發市場化,采用傳統電子設計手段在較短時間內完成復雜電子系統設計,已經越來越難完成了。EDA(EleCTRonICs Design Automation)技術是隨著集成電路和計算機技術飛速發展應運而生一種高級、快速、有效電子設計自動化工具。 1、EDA技術 EDA(電子線路設計座自動化)是以計算機為工作平臺、以硬件描述語言(VHDL)為設計語言、以可編程器件(CPLD/FPGA)為實驗載體、以ASIC/SOC芯片為目標器件、進行必要元件建模和系統仿真電子產品自

關鍵字:

EDA VHDL

這次我們講一講如何入門學習硬件描述語言和數字邏輯電路;學習數字邏輯電路,我推薦的一本書就是--《數字設計-原理與實踐》,其他的深入點可以看看《完整數字設計》;而對于硬件描述語言呢?有兩個原則,一個是買書的原則,一個是看書的原則。首先,你必須買兩類書,一類是語法書,平常使用的時候可以查一查某些語法;一類是,對語言的使用的講解和使用的方法(如何書寫RTL,如何設計電路,如何調試代碼,使用仿真器等);我用過一年的VHDL和兩年的Verilog;作為過來人,我想介紹一些比較好的書給入門者,避免大家走彎路。

關鍵字:

VHDL Verilog

引 言

電動機是各類數控機床的重要執行部件。要實現對電動機的精確位置控制,轉子的位置必須能夠被精確的檢測出來。光電編碼器是目前最常用的檢測器件。光電編碼器分為增量式、絕對式和混合式。其中,增量式以其構造簡單,機械壽命長,易實現高分辨率等優點,已被廣泛采用。增量式光電編碼器輸出有A,B,Z三相信號,其中A相和B相相位相差90°,Z相是編碼器的“零位”,每轉只輸出一個脈沖。在應用中,經常需要對A相、B相正交脈沖按照一定的比例,即分周比進行分頻。分頻的難點是,無論設定分

關鍵字:

FPGA VHDL

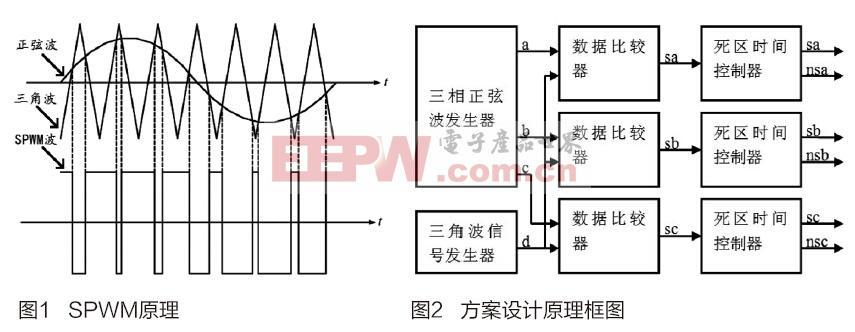

本文提出了一種采用VHDL硬件描述語言設計新型三相正弦脈寬調制(SPWM)波形發生器的方法。該方法以直接數字頻率合成技術(DDS)為核心產生三相SPWM信號。并且利用VHDL設計了死區時間可調的死區時間控制器,解決了傳統的模塊電路等待方法很難產生帶精確死區時間控制的SPWM信號的問題。該方法在Quartus II 9.1環境平臺下進行了仿真驗證,并將設計程序下載到DE2-70實驗板進行實驗測試,用示波器測試得到了死區時間可控制的SPWM波形。

關鍵字:

VHDL SPWM DDS 死區時間 FPGA 201505

引 言

FPGA 即現場可編程邏輯陣列。是在CPLD 的基礎上發展起來的新型高性能可編程邏輯器件。FPGA的集成度很高,其器件密度從數萬門到數千萬門不等,可以完成極其復雜的時序與組合邏輯電路功能,適用于高速、高密度的高端數字邏輯電路設計領域。新一代的FPGA 甚至集成了中央處理器( CPU ) 或數字處理器( DSP) 內核,在一片FPGA 上進行軟硬件協同設計,為實現片上可編程系統( SOPC) 提供了強大的硬件支持。對微型打印機的驅動,傳統方法是使用單片機是實現對其的時序控制。隨著FPGA

關鍵字:

FPGA VHDL

VHDL是隨著可編輯邏輯器件(PLD)的發展而發展起來的一種硬件描述語言。它是1980年美國國防部VHSIC(超高速集成電路)計劃的一部分,并于1986年和1987年分別成為美國國防部和IEEE的工業標準。作為一種硬件設計時采用的標準語言,VHDL具有極強的描述能力,能支持系統行為級、寄存器傳輸級和門級三個不同層次的設計,這樣設計師將在TOP-DOWN設計的全過程中均可方便地使用同一種語言。而且,VHDL設計是一種“概念驅動式”的高層設計技術,設計人員毋需通過門級原理圖描述電路

關鍵字:

VHDL

心率監控器是一款用于監測人體心跳速率的器件。心率的單位是bpm(每分鐘心跳數)。人體的心跳速率根據其日常身體活動、睡眠和基本健康狀況的不同而有所差別。本文為大家介紹幾種心率計及心率監測系統的設計,供大家使用參考。

基于EFM32TG840的便攜式心率計的設計方案

在消費電子領域,便攜式電子產品由于體積小、質量輕的特點越來越受到消費者的喜愛,已成為人們生活中不可缺少的部分。基于這個思路,我們設計了一款便攜式心率計,它可以替代用脈搏聽診器等進行測量的傳統方法,使用非常方便。

一種便攜式單

關鍵字:

FPGA VHDL

圖像傳感器,或稱感光元件,是一種將光學圖像轉換成電子信號的設備,它被廣泛地應用在數碼相機和其他電子光學設備中。早期的圖像傳感器采用模擬信號,如攝像管(video camera tube)。如今,圖像傳感器主要分為感光耦合元件(charge-coupled device, CCD)和互補式金屬氧化物半導體有源像素傳感器(CMOS Active pixel sensor)兩種。本文介紹基于CMOS或CCD兩種圖像傳感器的應用及技術文獻,供大家參考。

基于USB傳輸及CMOS圖像傳感器的指紋識別儀的實

關鍵字:

Verilog HDL QuartusⅡ VHDL

FIR濾波器,有限長單位沖激響應濾波器,又稱為非遞歸型濾波器,是數字信號處理系統中最基本的元件,它可以在保證任意幅頻特性的同時具有嚴格的線性相頻特性,同時其單位抽樣響應是有限長的,因而濾波器是穩定的系統。因此,FIR濾波器在通信、圖像處理、模式識別等領域都有著廣泛的應用。本文著重介紹基于不同結構的FIR濾波器的設計方案,供大家參考。

基于FPGA 的FIR 數字濾波器設計方案

基于FPGA分布式算法的低通FIR濾波器的設計與實現

二維FIR濾波器的FPGA實現

基于XC2V10

關鍵字:

Simulink VHDL EDA技

用CPLD設計所構成的CPI接口系統具有簡潔、可靠等優點,是一種行之有效的設計途徑。很多技術雜志和網站上,都有不少用CPLD設計PCI 常規傳輸系統的文章。但用這些方法在MzxPlusII、Fundition等環境下進行模擬仿真時,其產生的時序往往與PCI規范有很大出入。雖然 Altera 等公司推出PCI核可以直接使用,但這樣的內核占用CPLD資源較多,且能適配的器件種類少,同時價格也高,在實際設計應用中有很大的局限性。因此,使用通用型CPLD器件設計簡易型PCI接口有很大的現實意義。在Compac

關鍵字:

PCI VHDL-CPLD Compact接口

1引言

隨著社會的發展。使用電梯越來越普遍,已從原來只在商業大廈、賓館過渡到在辦公室、居民樓等多種建筑中,并且對電梯功能的要求也不斷提高,其相應控制方式也在不斷發生變化。電梯的微機化控制主要有:PLC控制、單板機控制、單片機控制、單微機控制、多微機控制和人工智能控制等。隨著EDA技術的快速發展,PLD器件已廣泛應用于電子設計與控制的各個方面。這里使用CPLD器件,采用VHDL語言設計一個16樓層單個載客箱的電梯控制系統,此控制系統具有使用安全可靠,功能全面的特點,方便人們生活。

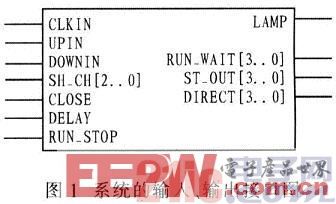

2系統總體

關鍵字:

CPLD VHDL 電梯

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件(PLD)的發展而發展起來的。它是一種面向設計、多層次的硬件描述語言,是集行為描述、RTL描述、門級描述功能為一體的語言,并已成為描述、驗證和設計數字系統中最重要的標準語言之一。由于VHDL在語法和風格上類似于高級編程語言,可讀性好,描述能力強,設計方法靈活,可移植性強,因此它已成為廣大EDA工程師的首選。目前,

關鍵字:

FPGA CPLD VHDL

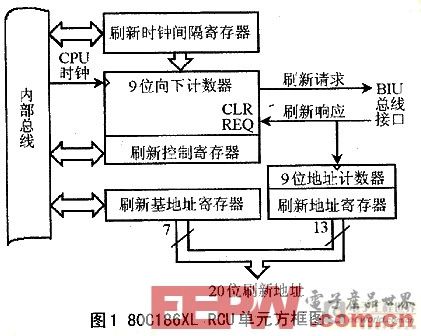

80C186XL16位嵌入式微處理器是Intel公司在嵌入式微處理器市場的上導產品之一,已廣泛應用于電腦終端、程控交換和工控等領域。在該嵌入式微處理器片內,集成有DRAM RCU單元,即DRAM刷新控制單元。RCU單元可以自動產生DRAM刷新總線周期,它工作于微處理器的增益模式下。經適當編程后,RCU將向將處理器的 BIU(總線接口)單元產生存儲器讀請求。對微處理器的存儲器范圍編程后,BIU單元執行刷新周期時,被編程的存儲器范圍片選有效。

存儲器是嵌入式計算機系統的重要組成部分之一。通常采用靜態

關鍵字:

CPLD DRAM VHDL

vhdl 介紹

VHDL的英文全名是Very-High-Speed Integrated Circuit HardwareDescription Language,誕生于1982年。1987年底,VHDL被IEEE和美國國防部確認為標準硬件描述語言 。自IEEE公布了VHDL的標準版本,IEEE-1076(簡稱87版)之后,各EDA公司相繼推出了自己的VHDL設計環境,或宣布自己的設計工具可以和VHDL接口。此后 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473