基于FPGA和萬兆網(wǎng)的GigE Vison設(shè)計(jì)方案

基于FPGA和萬兆網(wǎng)的GigE Vison設(shè)計(jì)方案

作者:Hello,Panda

本文簡要描述基于萬兆網(wǎng)的GigE Vison IP設(shè)計(jì)方案。

一、GigE Vsion協(xié)議要點(diǎn)

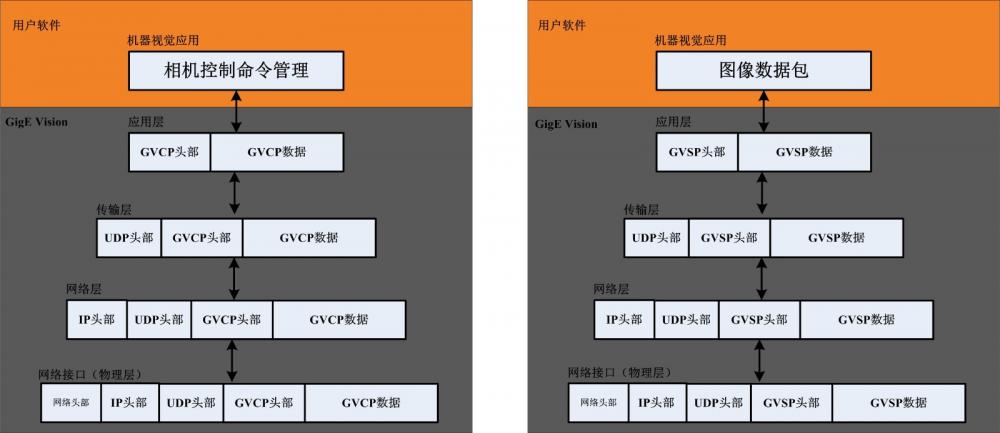

GigE Vison協(xié)議基于普通的以太網(wǎng)物理鏈路,運(yùn)行在UDP協(xié)議層之上,包含控制協(xié)議GVCP和數(shù)據(jù)流協(xié)議GVSP兩大部分,整個(gè)層次結(jié)構(gòu)如下圖1所示。

圖1 GigeVison協(xié)議層次結(jié)構(gòu)圖

GigE Vison協(xié)議的要點(diǎn)如下:

(1)上電或復(fù)位完成后必須先進(jìn)行IP配置和設(shè)備枚舉,必須支持DHCP和LLA(Auto IP)兩種IP配置方式;

(2)在UDP層上建立應(yīng)答握手機(jī)制以保證傳輸,GVCP采用3956端口,數(shù)據(jù)長度必須以32bit為邊界,數(shù)據(jù)不可分包傳輸;

(3)設(shè)備必須支持心跳功能以確認(rèn)處于連接狀態(tài);

(4)支持控制(1個(gè))、數(shù)據(jù)流(1~512個(gè))和消息(0~1個(gè))三種通道,每個(gè)通道分配不同的UDP端口,控制通道支持三種不同的訪問權(quán)限;

(5)必須支持最小規(guī)模的ICMP(GigeVsion要求必須支持Ping命令);

(6)GVSP的數(shù)據(jù)包以字節(jié)為邊界,數(shù)據(jù)包的大小由第一個(gè)有效的test packets決定,支持錯(cuò)誤恢復(fù)和流控制;

(7)GVSP數(shù)據(jù)傳輸?shù)膯挝粸?/span>Block,一個(gè)完整的Block由Data Leader、Data Payload和Data Trailer構(gòu)成;

(8)所有的Gige Vison相機(jī)都必須在他們的XML描述文件中強(qiáng)制制定相機(jī)的參數(shù)信息。

(9)bootstrap寄存器及XML文件需要非易失Flash硬件支持。

二、IP功能設(shè)計(jì)方案要點(diǎn)描述

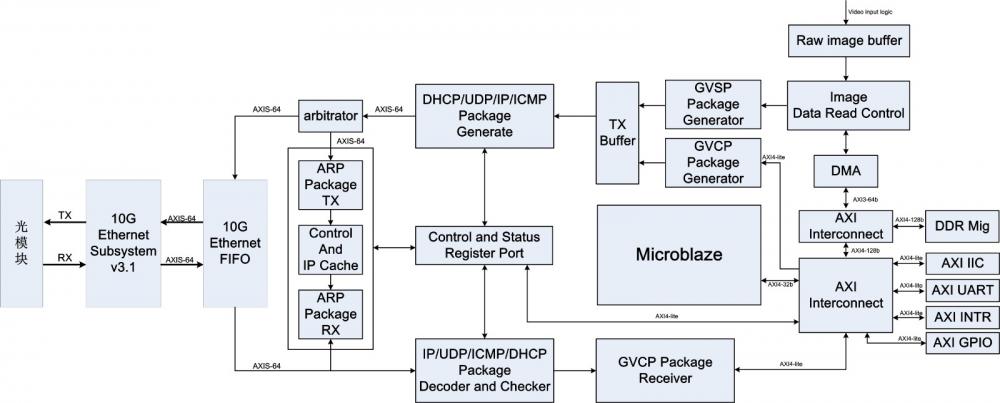

GigE Vison邏輯IP需要實(shí)現(xiàn)圖1所示的所有協(xié)議層,方案中硬件平臺基于Xilinx 7系列器件XC7K325T/XC7K160T,下圖2是GigE Vision IP核的模塊框架結(jié)構(gòu)。

圖2 GigE Vision IP核的框架結(jié)構(gòu)

(1)物理層

物理層使用Xilinx 10G Ethernet Subsystem IP核,版本v3.1。對外數(shù)據(jù)接口例化為AXI4 Stream,位寬64bit,數(shù)據(jù)時(shí)鐘156.25MHz;配置接口例化為AXI4-Lite,位寬32bit,時(shí)鐘頻率100MHz。

IP核配置通過Microblaze軟核完成,并且使能Jumbo幀功能。功能、接口、配置和使用說明參見Xilinx官方文檔PG157。

(2)IP/UDP層

IP層協(xié)議僅支持IPv4版本,IP數(shù)據(jù)報(bào)頭Options項(xiàng)為空;需要支持DHCP、ARP和ICMP協(xié)議,內(nèi)部通信采用64位AXI4 Steam總線通信。

(3)GVCP/GVSP協(xié)議

支持GigE Vison Specification version 1.0標(biāo)準(zhǔn)描述的所有必須支持的項(xiàng),GVSP數(shù)據(jù)包負(fù)載類型支持Payload type = RawData/YUV422-8bit/RGB888。為完整實(shí)現(xiàn)功能,部分控制放在處理器上完成(本設(shè)計(jì)實(shí)例使用MicroBlaze),需要掉電保存的項(xiàng)存儲在外部Flash中,需要大量緩存的數(shù)據(jù)存儲在片外DDR中。

RTL描述語言使用Verilog,編譯工具使用Xilinx Vivado2016.4,仿真工具使用ModelSim 10.2C。

備注:

(1)為簡化邏輯端的設(shè)計(jì)難度,可將GVCP協(xié)議放在Microblaze里面實(shí)現(xiàn),使用ZYNQ系列器件的,可以直接在PS里運(yùn)行;

(2)物理層使用千兆網(wǎng)的,本方案仍然可行,只需修改物理層接口即可;使用ZYNQ系列器件的,可以直接在PS里軟件實(shí)現(xiàn)所有的GVCP和GVSP協(xié)議;

三、測試結(jié)果

在Xilinx K7 325T器件上實(shí)現(xiàn)完整的系統(tǒng)(包括DDR Mig、Microblaze等),占用Slice約30K。

與PC進(jìn)行點(diǎn)對點(diǎn)數(shù)據(jù)傳輸測試,穩(wěn)定傳輸速率約為6.5Gbps,可輕松傳輸4K無壓縮原圖或一些特殊圖像數(shù)據(jù)如超聲、CT、雷達(dá)、高速ADC采樣結(jié)果等原始數(shù)據(jù)。

*博客內(nèi)容為網(wǎng)友個(gè)人發(fā)布,僅代表博主個(gè)人觀點(diǎn),如有侵權(quán)請聯(lián)系工作人員刪除。

linux操作系統(tǒng)文章專題:linux操作系統(tǒng)詳解(linux不再難懂)