繞開先進制程封鎖!中國“小芯片”標準草案即將公示,獨家對話郝沁汾

編輯 | 漠影

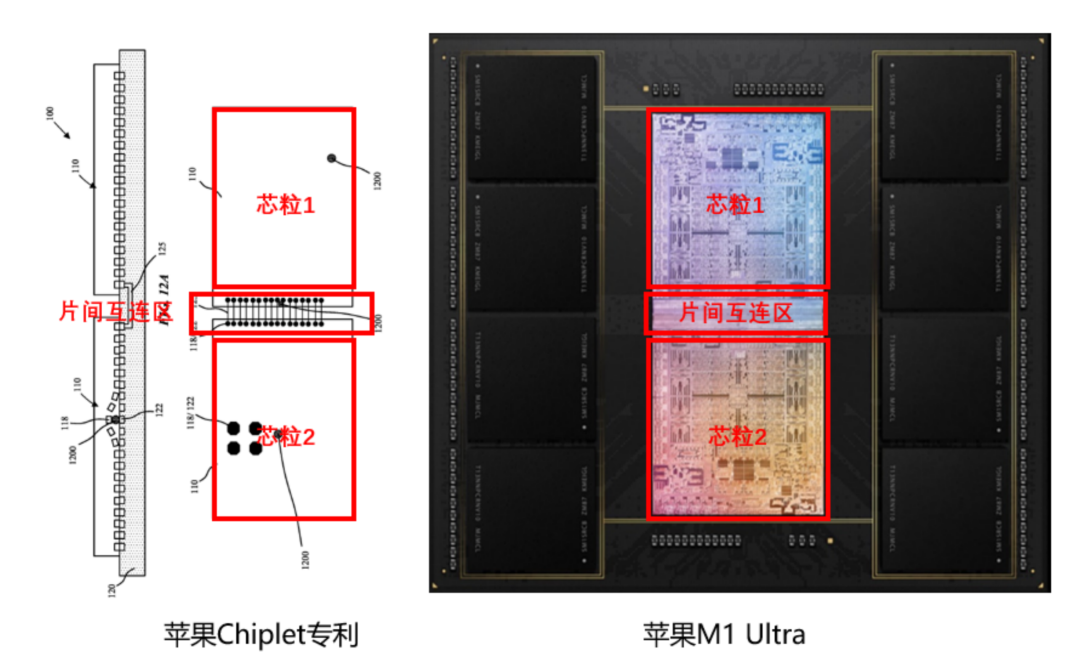

2022年3月,Chiplet儼然成為巨頭擁躉的焦點。3月2日,英特爾、AMD、Arm、臺積電、三星、日月光、高通、微軟、谷歌云、Meta十家巨頭聯合,發起一項瞄準chiplet的新互連標準UCIe。僅隔一周,蘋果又甩出了一個性能爆表的頂級電腦芯片M1 Ultra,其中將兩枚M1 Max芯片“粘連”而成的“膠水”封裝****,同樣屬于chiplet技術范疇。這兩起事件,直接將chiplet的熱度推至高潮。

▲蘋果Chiplet專利與M1 Ultra芯片(參考專利US 20220013504A1)

值得注意的是,擁有頂級芯片設計水平的蘋果,并未出現在UCIe標準的首發成員名單中,其M1 Ultra芯片的實現方式,也與UCIe不同,反倒與我國正在推進的chiplet標準在目的和功能上有些類似。標準的制定對于生態的擴張至為關鍵,但多位業內專家或資深人士告訴芯東西,UCIe標準對國內產業的價值還很模糊,尤其在全球科技“武器化”和美國政府提防中國科技崛起的地緣沖突背景下,這個新標準預計很難為國內廠商提供助力。芯東西獲悉,國內chiplet標準草案現已制訂完畢,即將進入征求意見階段,預計第一季度掛網公示和意見征集,第二季度完成技術驗證計劃制訂,年底前完成技術驗證,并完成標準文本的確定,進行初版標準的發布工作,首個版本發布即可用。那么,國內外標準存在哪些異同?這些標準的建立會怎樣影響后摩爾時代芯片的發展格局?推進此類標準的建設,還需突破哪些障礙?圍繞這些問題,近日,芯東西與無錫芯光互連技術研究院院長、無錫芯光集成電路互連技術產業服務中心主任、中國計算機互連技術聯盟秘書長、中科院計算所研究員郝沁汾進行深入交流,解讀chiplet標準建設背后的痛點、趨勢與隱憂。芯謀研究分析師張先揚亦為本文貢獻了有價值的行業觀點。

▲無錫芯光互連技術研究院院長、無錫芯光集成電路互連技術產業服務中心主任、中國計算機互連技術聯盟秘書長、中科院計算所研究員郝沁汾

01.Chiplet:摩爾定律的“救星”

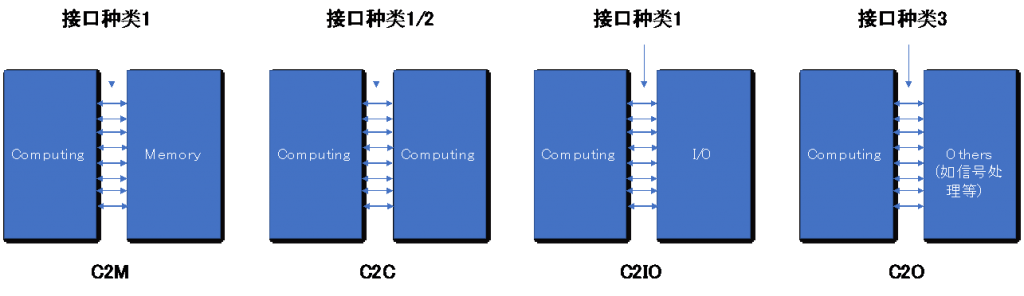

▲部分集成電路互連技術種類示意圖

2015年,Marvell創始人周秀文在ISSCC 2015上提出MoChi(模塊化芯片)架構概念。隨后,AMD率先將chiplet應用于商業產品中。相比之下,英特爾切入這一技術方向的時間稍晚。2020年1月,英特爾加入由Linux基金會主辦的美國CHIPS聯盟,并免費提供了AIB互連總線接口許可,以支持chiplet生態系統的建設。但由于需使用英特爾自家的先進封裝技術EMIB,AIB標準未能廣泛普及。今年3月,英特爾又牽頭發起一項chiplet新標準,即開篇提到的UCIe標準。

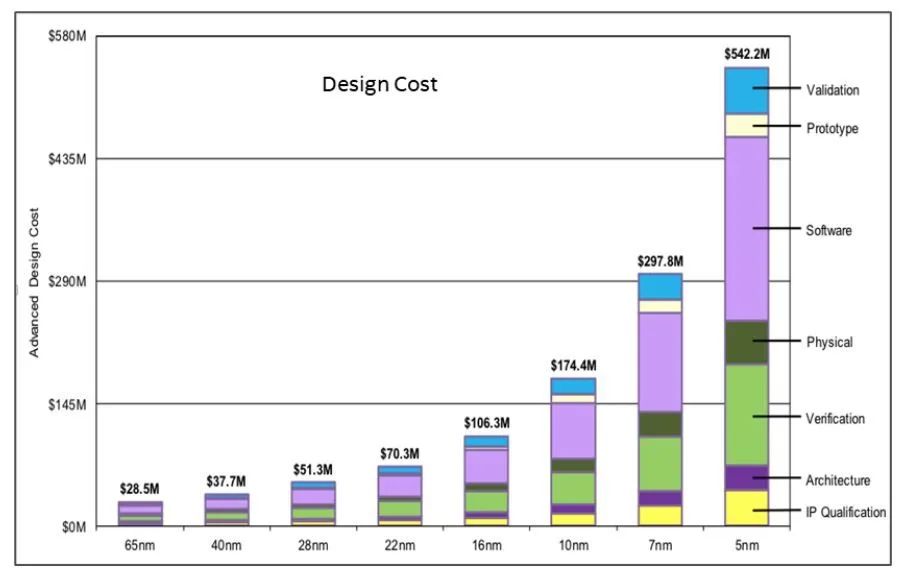

▲隨著先進制程演進,芯片設計成本飆升

相比單芯片設計,基于chiplet設計的芯片,可以進一步提升良率,降低成本,同時性能更強。一顆芯片上有不同功能的模塊組件,如果全用最先進的技術節點來制造,成本會非常高。而多顆小芯片封裝在一起,通過讓不同功能的芯片模塊分別選用合適的制程工藝,不僅可在技術方面實現各功能的最優化,合理利用先進工藝提升那些能夠獲益的芯片內容,也能進一步節約生產成本,提升所設計芯片的總體性價比。除此之外,芯片面積越大,良品率越低。比如150mm2芯片的良品率有80%,到700mm2已經低至30%。Chiplet采用多顆小芯片組合的思路,以更小的裸片提升總體良率,可以帶來更高的硅利用率和產能。因此,芯片業已經不再只關注單裸片芯片,而是開始將多個裸片組成的單個芯片集成到系統中,并有越來越多的芯片公司投入相關研發。但隨著基于chiplet的芯片品類逐漸多樣,缺乏標準的問題逐漸變得棘手。02.不僅要建立標準還必須建立國內原生標準

▲UCIe聯盟首批成員名單

在郝沁汾看來,英特爾牽頭這些標準的核心動力,是維護和豐富其生態系統的完整性。UCIe標準明確提出支持CXL和PCIe協議,而這兩個互連協議均由英特爾提出和創建。例如,PCIe是x86系統主要的IO總線標準,所有IO設備必須支持PCIe才能和X86 CPU相連。由于目前很多加速器芯片的計算能力,已經可以和主CPU相提并論,因此CXL在IO模式基礎上,又新增了CXL.mem和CXL.cache的模式,以適應技術形勢的發展。值得注意的是,UCIe聯盟的初始成員名單中,沒有蘋果、英偉達等芯片圈知名“狠角色”,也完全沒有中國大陸廠商的身影。英偉達可能是因為其業務高毛利,對成本不敏感,暫時對chiplet這種設計方式不太感興趣,再加上英偉達有自己的片間互連協議NVLink,與英特爾對數據中心場景的一些期望不一致,因此支持UCIe與否不是必須為之。而蘋果上周最新發布的電腦芯片M1 Ultra,已是在chiplet方向上的一次成功嘗試。至于面向國內芯片企業,有一個問題值得商榷:UCIe標準的“開放”,究竟是何種程度的開放?

▲UCIe的介紹是一個開放的行業標準互連

“我們認為的開放,應該是從標準的協議到參考實現都是開放的,但是我們看到英特爾所標榜的這些標準,從PCIe到CXL、AIB和UCIe,實現參考設計所需要的技術細節,你都在標準協議中找不到的。”郝沁汾曾向另一家更早開展chiplet互連標準制定的美國組織ODSA寫郵件詢問,還托以前的同事去交流,結果對方明確告知,該標準中很多涉及實現的技術細節是不能對中國開放的。這與美國政府的“視同出口”規定有關,美國企業假如沒有申請出口許可就將技術輸向海外,哪怕只是在標準會議中的技術探討,都屬于違規。因此,在中美關系仍較為緊張的情況下,美國技術聯盟如果貿然將大陸廠商拉進去,會承擔法規方面的風險。“標準有國界”的警鐘三年前就敲響過。2019年5月,美國商務部宣布將華為列入實體清單,隨后PCIe組織PCI-SIG曾短暫地停掉華為的會員資格。再結合近期的俄烏戰事,可以看到科技已經“武器化”,假如哪天美國政府再次升級技術出口管制措施,依賴國際標準的國內企業可能要吃些苦頭。在芯謀研究分析師張先揚看來,UCIe的出現,代表著全球半導體產業已經進入到成熟的產業階段。但UCIe是否具有持續的市場前景,主要看未來chiplet與高度集成的單片芯片是否會形成差異化的市場結構,這一點很像大家在討論的ASIC和FPGA誰是最終歸屬的問題。此外,UCIe產業聯盟成員基本可形成一個小的產業生態閉環,這將進一步提高各產業環節的集中度,并鞏固了龍頭優勢,是否會真正利好半導體產業的發展也是存疑的。“尤其需要注意到英特爾在美國半導體產業中扮演的敏感角色,在此特定背景下,我們不希望看到UCIe會成為政治化的工具。”他告訴芯東西。張先揚認為,國內方面,我們要繼續走好自己的路,在加速國產化替代的同時,做好應對一切沖擊的準備,UCIe提供了一種可參考的產業平臺機制,我們亦可以通過組建內部產業聯盟的方式來優化產業分工,進一步加快國內產業發展,提高國內半導體產業對于沖擊的耐受力。這也是郝沁汾決定另起爐灶,在國內構建一套原生chiplet標準的初衷。03.國內外chiplet標準有何異同?

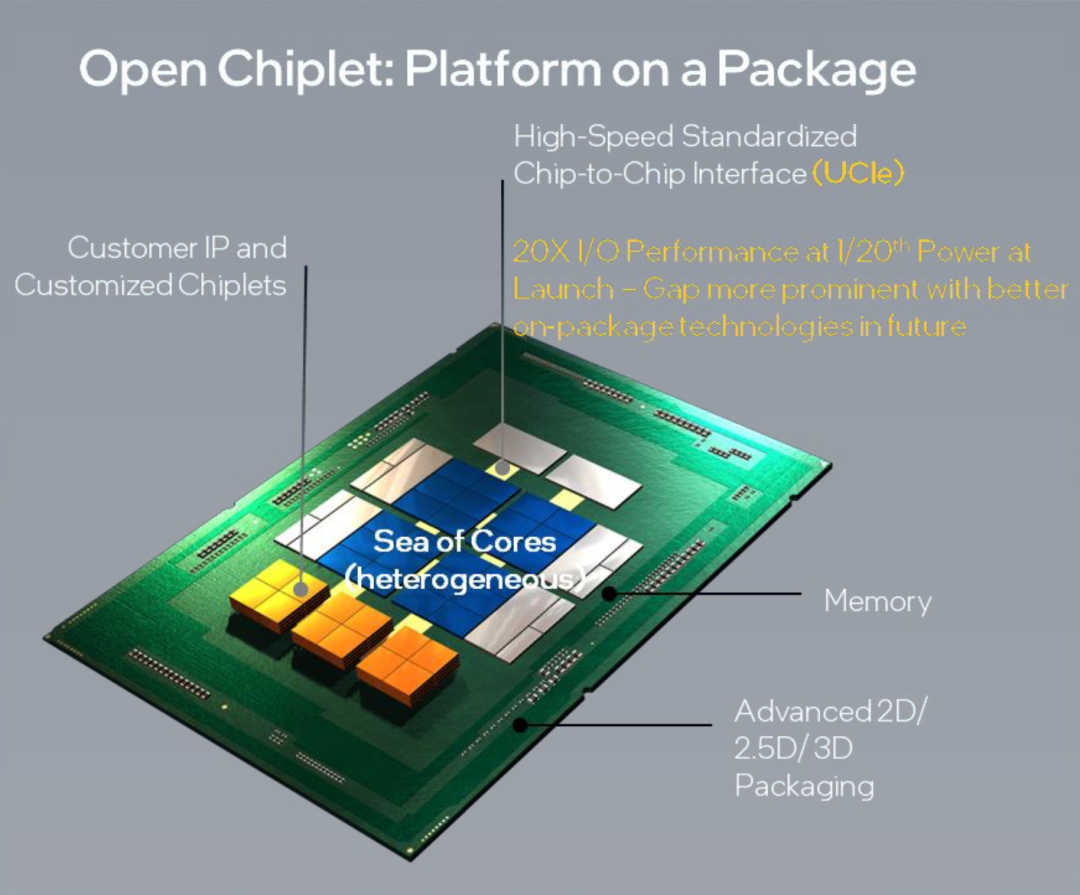

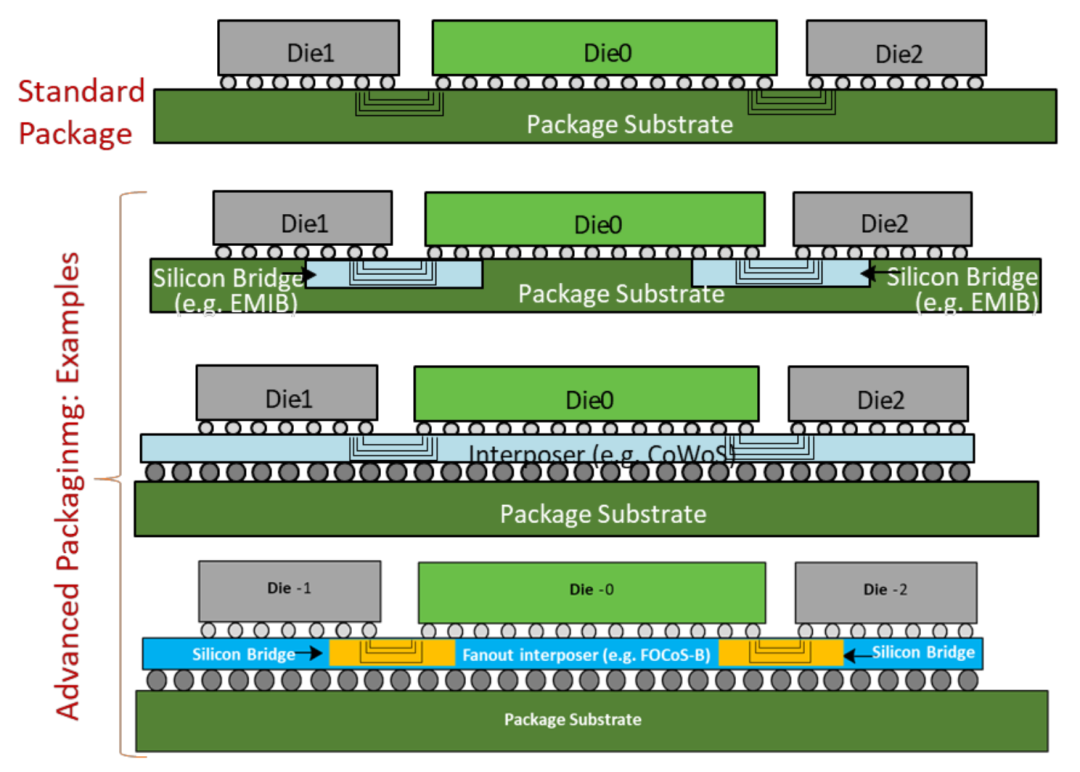

▲UCIe支持的封裝方式

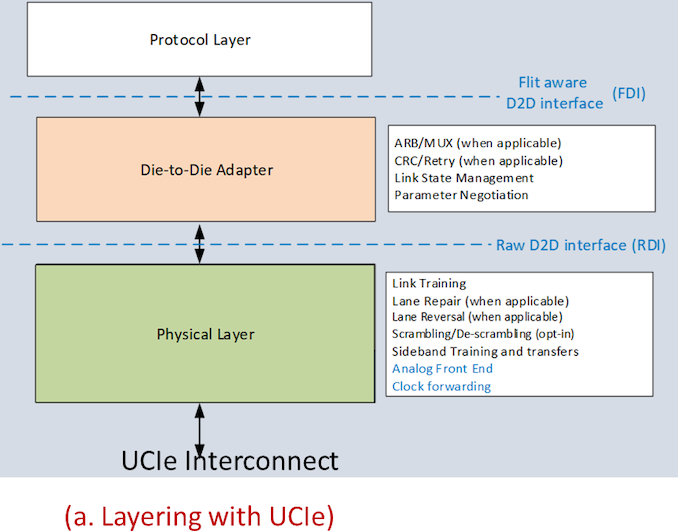

在郝沁汾看來,先進制程停滯背景下,chiplet面臨著很好的機會,但我國面臨的最現實問題,不是先進制程停滯,而是先進制程被禁運了怎么辦?戰略風險在于,倘若UCIe支持的三種先進封裝技術被禁運,大陸廠商想用UCIe協議,只能采用標準封裝的方式。而采用標準封裝方式的chiplet間互連帶寬,僅有采用先進封裝帶寬的1/6,性能大幅縮水。在標準組成上,UCIe主要由D2D適配層、物理層(含封裝)組成,圖中虛線以上是既有協議,CXL或PCIe。我國的《小芯片接口總線技術要求》也有類似的組成,由鏈路適配層、物理層及封裝組成。

▲UCIe分層協議的組成

兩個標準的關鍵區別之一在于,UCIe在D2D組成的芯片中,加入了一種叫retimer的功能芯片定義,它負責把信號由并行轉成串行,然后以更高速度傳送到較遠的地方。郝沁汾談道,這個目的主要是為了實現英特爾自身在數據中心中CPU和內存解耦、資源池化方案。國內《小芯片接口總線技術要求》則不包括這部分內容,而是一個純粹的D2D互連標準。郝沁汾認為,我國的標準更加符合國情。比如在物理層,國內chiplet標準同時支持單端信號和差分信號,單端的信號是一根線,差分信號是一對線,可以把信號傳的更遠一點。通過chiplet將兩個芯片互連,只要支持差分信號,就能使國內某些加速器芯片廠商實現將相同的芯片通過差分信號接口相連,以拓展總體性能的目的。這種先用成熟工藝做出小芯片、再用先進封裝技術把它們拼在一起的方式更加廉價經濟,可替代采用7nm、5nm先進制程工藝生產芯片的昂貴方案。上周蘋果最新推出的最強電腦芯片M1 Ultra,其實現方式與國內的chiplet標準更為類似。而UCIe只支持通過單端信號實現D2D互連,與國內廠商的現階段訴求不一致,實用性欠佳。郝沁汾告訴芯東西,國內chiplet標準既支持像臺積電CoWoS等先進封裝方式,也支持國內先進封裝方法的最新積累,這樣國內企業萬一被施加技術限制,至少還有個備用方案,而不至于措手不及。04.chiplet是我國必須抓住的技術機會

05.結語:路漫漫其修遠兮

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。