基于通道控制的雙余度DSP設計與實現

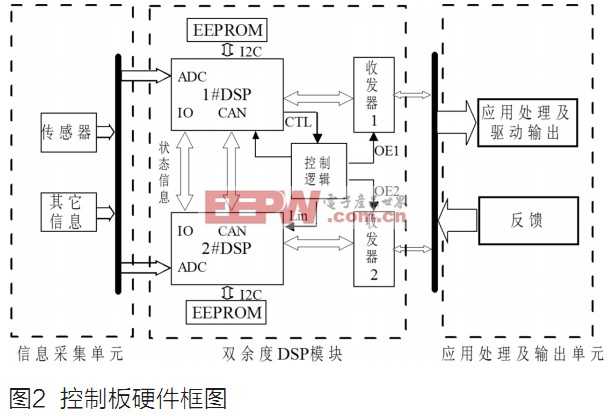

雙余度DSP模塊硬件設計

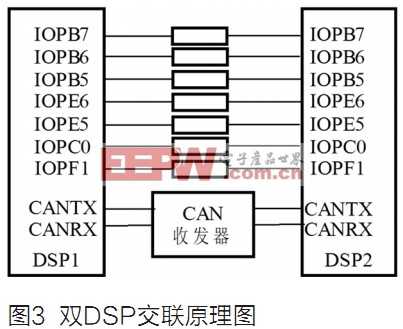

雙余度DSP模塊是本設計的重點,其硬件原理如圖2的雙余度DSP模塊。它由雙DSP核及通道控制邏輯兩部分組成。其中DSP1為主CPU,DSP2為輔CPU。當系統上電啟動后主CPU通過I/O口通知輔CPU進行自檢并采集其自檢信息,同時當主CPU的EEPROM內容發生改變時,主CPU通過CAN總線發送相應的數據給輔CPU以更新輔CPU的EEPROM內容,如圖3所示。圖中CAN收發器為兩個對連的CAN總線收發器,負責實現雙機間系統即時信息的傳送,并存儲于各自對應的EEPROM中,供維護和查詢。

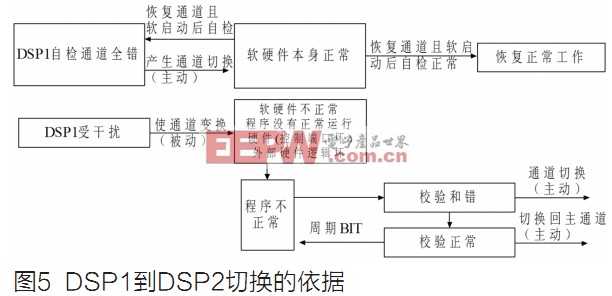

通道控制邏輯決定著整個系統的當前工作CPU,即當其中一個CPU被認為有故障時,通道控制邏輯將主動或是被動地切換到系統認為沒有故障的CPU,或決定由其中的一個CPU強制工作。通道控制邏輯的硬件原理如圖4所示。所謂的主動切換是指當主DSP通個自檢發現自身有故障(包括其對應的通道故障),而其程序能正常工作的情況下,由其程序產生的通過控制I/O口的邏輯電平而產生的通道切換。被動切換是指非DSP自檢的因素產生,而是由于通道控制邏輯本身硬件故障引起的通道意外切換。通道控制邏輯硬件由門電路組成,能有效地防止雙機的搶權問題。同時控制邏輯返回給兩個DSP一個“CTL_BACK”狀態回讀信號,用于判斷當前的通道情況。

主DSP通過控制輸入端口的邏輯狀態來使能相應的通道,只有當兩個控制端同時有效時選通主通道,此時主DSP工作。其他任何狀態都將打開輔通道。可以有效避免由于主控DSP I/O口失效而產生不能切換的后果。同時主DSP不斷檢測“CTL_BACK”狀態回讀信號的狀態,否則將產生被動切換,說明通道控制邏輯硬件故障。輔DSP上電后不斷檢測“CTL_BACK”狀態回讀信號,若檢測到為有效,則說明通道已經切換到了輔通道,輔DSP開始工作。

評論