手把手課堂:Xilinx FPGA設計時序約束指南

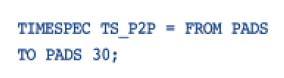

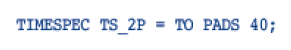

若不選定時間單位(納秒、皮秒等),則工具將自動默認為納秒。例如,可這樣寫約束:

本文引用地址:http://cqxgywz.com/article/119144.htm

也可只寫From 或 只寫To ,以使其更具一般性:

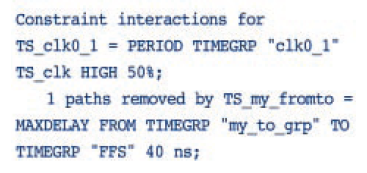

如前所述,工具將自動默認上文所述所有 FROM: TO 約束的優先級高于PERIOD 約束,除非另有規定。

除幫助查看時序約束迭代外,.tsi 報告還就如何改進通用約束文件 (UCF) 中的約束提供方法建議。該報告還會告知是否有路徑受多重時鐘域的約束。下面是約束迭代報告的例子:

在本例中,高優先級的 FROM: TO約束(僅一個)將優先于 PERIOD 約束應用。

建立和保持

在實際的同步數字系統中,數據必須先于進行采樣的時鐘脈沖邊沿到達。達到這一目標所需的最短時間稱為“建立時間”。除了先于時鐘脈沖邊沿到達外,數據必須在時鐘脈沖邊沿保持一定時間,這一時間稱為“保持時間”。保持時間可

以為負,此時數據在時鐘脈沖邊沿到達前便已結束;可以為零,此時數據保持到時鐘脈沖邊沿采樣;也可為正,此時數據保持到時鐘脈沖邊沿采樣完畢后一段時間。

根據設計,在 FPGA 架構中,對所有速度等級,保持時間均不為正(或零或負)。這樣可簡化布局和布線,因數據只

需先于時鐘脈沖邊沿到達,并可在時鐘脈沖邊沿采樣發生后即刻發生變化。數據超出最小建立時間的值稱為時序裕量。時序裕量應總是為正。若報告上出現時序裕量負值,則說明建立時序尚未得到充分滿足,數據到達太遲。

時鐘路徑本身也有延遲或偏移。因此,要分析時序,工具需計算出數據和時鐘到達所分析觸發器的時間。

約束違例的簡便補救辦法

重申一下:PERIOD 約束定義的是觸發器等同步元件的時鐘周期。可使用時序分析器來驗證同步元件之間的所有路徑是否滿足設計的建立和保持時序要求。PERIOD 約束違例將以負的時序裕量顯示在在時序報告,并說明到底是建立時間還是保持時間要求出現違例。所以若報告顯示發生了建立時間違例時該作何處理?應找出兩個所分析的同步元件間一條較快路徑,或至少是某種方法來確保數據在合適時間內到達并保持足夠長的時間,以便時鐘脈沖邊沿能夠正確采樣。若布局布線軟件無法找到更快的路徑,則可從 FPGA Editor 工具中手動進行布線。

不過這是最后的手段。在弄清楚不用它如何解決問題之前,請盡量不要使用這種方法。只使用 FPGA Editor 查看底層結構“知其所以然”,了解工具對設計的所做的處理,以達到讓設計恰當的使用FPGA 資源來實現的目的。首先試試重構電路來滿足設計的時序要求。一個比較簡單的方法就是在路徑上及早布置一個觸發器。該技術即為流水線,它會增加信號的延遲,不過也可使信號值得到正確地采樣。

若出現保持時間違例(數據在時鐘脈沖邊沿到來之前便已結束),則往往說明存在設計問題(架構不良)。數值只能

在時鐘脈沖邊沿發生變化,而不是之前。

若外部信號值在時鐘脈沖邊沿之前發生變化,則需使用 DCM 或 PLL 延遲時鐘脈沖邊沿,這樣數據才能由新的延遲時鐘正確采樣。

有一種替代方法,就是在輸入/ 輸出模塊中使用 IDELAY 元件,將數據移到時鐘有效的位置上。

數據有效窗口與亞穩態時鐘脈沖邊沿之前的時間(建立)加上時鐘脈沖邊沿之后的時間(保持)即為“數據有效窗口”,也就是數據保持穩定,以進行正常采樣的時間。若數據在此期間沒有保持有效,則結果存在不確定性,或不可知。

不過,數據的有效時間未達到規定的長度,并不意味著觸發器輸出為亞穩態。亞穩態不同于不確定。若不能滿足時序要求,則輸出可能為隨機的 1 或 0。亞穩態是指時鐘脈沖邊沿“幾乎”能進行狀態采集,而觸發器輸出則在時鐘脈沖邊沿之后的一段時間內處于某種中間狀態(非 1 非 0)。亞穩態無法避免,因其為時鐘脈沖邊沿和數據幾乎完全“錯過”時的電路物理狀態。

在設計合理的同步系統中,亞穩態不是什么問題。當出現異步情況(如敲擊鍵盤上的一個鍵)或當兩個同步時鐘彼此異步時,亞穩態就會成為問題。一般而言,若出現異步情況,則需進行同步處理。

關于如何處理亞穩態的情況,這里有篇不錯的專題文章: http://www.stanford.edu/class/ee183/handouts_

spr2003/synchronization_pres.pdf 。(要深入了解亞穩態,請查看本期第二篇文章 FPGA101)

fpga相關文章:fpga是什么

評論