滿足28 nm迫切的低功耗需求

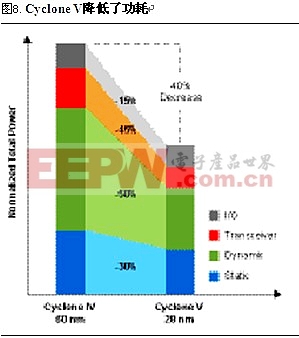

通過這些靜態和動態功耗優化措施,Altera基于28LP的FPGA總功耗比前幾代器件降低了40%,全面降低了功耗,如Cyclone V降低了功耗所示。

本文引用地址:http://cqxgywz.com/article/136059.htm

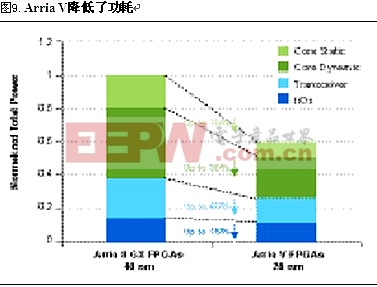

顯示了Arria V器件相似的結果。

通過軟件創新降低功耗

在工藝和體系結構創新基礎上,Altera在Quartus II的軟件功耗優化方面進行了大量的投入。功耗驅動的編譯使用功耗驅動綜合和功耗驅動布局布線功能,主要用于降低設計的總功耗。對于設計人員而言,這種功耗驅動的方法是透明的,通過簡單編譯設置來實現。設計工程師將時序約束簡單地設置為設計輸入過程的一部分,對設計進行綜合,滿足性能要求。Quartus II為每一功能模塊自動選擇所需的性能,并通過功耗預知布局布線和時鐘技術來降低功耗,如包括自動功耗優化的Quartus II設計流程所示。

評論