采用低功耗28-nm FPGA降低系統總成本

例如,一個簡單視頻處理應用只需要9位精度,而一些高端彩色系統則需要24位。對于9位視頻應用,一個模塊可以分成三個9位乘法器,將DSP模塊的效率提高了三倍。一個精度可調模塊能夠高效的滿足所有這些范圍要求。從而支持設計人員讓FPGA資源來適應其算法,而不是讓算法來適應有限的資源要求。

本文引用地址:http://cqxgywz.com/article/136063.htm硬核IP實現了高性能,提高了靈活性,而且縮短了設計時間

Altera在固定硅片中增強了某些常用的IP模塊(例如,雙倍數據速率存儲器控制器、協議堆棧,甚至是嵌入式ARM處理器),釋放寶貴的可編程邏輯資源,用于實現其他邏輯功能,從而提高了性能,降低了功耗和成本。作為一個例子,PCI Express® (PCIe®)協議堆棧需要大約150K LE作為軟核實現,在硬核模塊中則只需要三分之一的器件面積。采用競爭技術和工具嘗試實現PCIe內核的用戶會發現,使用Altera硬核IP結合Qsys系統集成工具,在設計和調試時間上平均能夠節省6個星期的時間。這對于設計團隊而言意味著大幅度降低了成本。

Altera還在FPGA中引入了第一種PCIe多功能支持。這一技術簡化了不同外設之間對PCIe鏈路帶寬的共享。支持8種功能,PCIe多功能支持將多個單一功能端點集成到一個多功能端點中。這縮短了開發時間,能夠節省20K LE。

利用PCIe多功能,設計人員能夠很好的定制業界標準處理器和駐留在FPGA邏輯中特有的多種外設。而且,支持多功能后,設計人員可以使用標準操作系統(OS)驅動軟件,在FPGA的外設上共享PCIe鏈路帶寬。沒有多功能支持時,開發過程中的一項主要工作是定制驅動軟件以實現這種資源共享功能。而且,多功能支持不需要多個軟核或者硬核PCIe內核,將其集成到了一個多功能PCIe端點中,從而有效降低了成本。

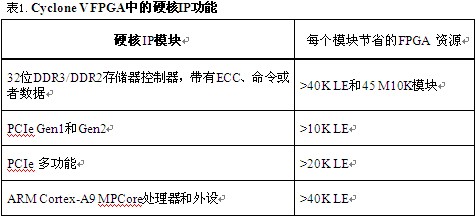

硬核IP最早出現在Altera的40-nm器件中,作為PHY層單元,因此,不再需要外部高性能串行I/O電路板元器件。在Altera 28-nm器件中,嵌入式硬核IP模塊實現了ASIC的成本、性能和功耗特性,不會犧牲設計靈活性。例如,可以在Cyclone V GT器件中配置PCIe硬核IP模塊來支持PCIe Gen1或者Gen2。此外,Cyclone V FPGA還提供兩個硬核PCIe內核——是競爭器件的兩倍。與軟核邏輯實現相比更強的優勢是,硬核IP模塊功耗降低了65%,而性能提高了50%,表1列出了Cyclone V FPGA中的硬核IP功能,以及通過硬核實現所節省的資源量。

成熟可靠的收發器,針對各種數據速率進行了優化,縮短了調試時間

Altera的28-nm系列產品引入了模塊化收發器,支持設計人員滿足實際應用的器件性能需求。在Altera所有28-nms FPGA系列中,這種收發器使用了相同的基本體系結構,最大工作速率從3.125-Gbps直至28-Gbps。正如Stratix V和Arria V器件一樣,Cyclone V收發器能夠在幾種不同的速率設置之間動態切換,可以降速來降低功耗。這種選擇功能為降低系統平均功耗提供了一種方法,在空閑時,收發器工作在最小速率,根據需要切換到高速工作。

如果I/O擴展等應用只需要5-Gbps或者速率更低的收發器,那么,不會出現28-Gbps工作時大型晶體管那樣的功耗和成本。相反,收發器以最低功耗和最低成本實現了3.125-Gbps和5-Gbps性能,Cyclone V FPGA系列能夠很好的適應設計。與Stratix V和Arria V器件中的收發器相似,Cyclone V FPGA收發器支持多種協議,包括,3G SDI、千兆以太網(GbE)、CPRI、Display Port、PCIe、Serial ATA (SATA)和Serial RapidIO®等。Altera收發器信號完整性以及通過收發器工具包實現的實時調試功能,能夠節省數星期的電路板開發和調試時間。

f 關于收發器工具包的詳細信息,請參考Altera網站的收發器工具包頁面。

僅采用兩種電壓軌,簡化了電源分配,降低了成本

在所有低成本FPGA中,Cyclone V FPGA需要的電壓軌數量最少。它們有內置片內電壓穩壓器,因此,您只需要使用兩種電壓軌來同時支持邏輯和收發器電源。這樣,可以不需要板上電壓穩壓器,避免了布線擁塞,減少了所需的電路板層數,從而簡化了電路板設計。競爭器件至少需要三種電壓軌來支持內核、I/O和收發器邏輯。額外的電源軌需要增加元件以及PCB面積,還可能會帶來布線擁塞問題,因此,在您的電路板開發預算中,成本可能會增加10到30美元。

fPLL可合成任意頻率,不需要額外的振蕩器

Altera 28-nm器件的通用鎖相環是fPLL,它具有高級分段式頻率合成以及M/N頻率實現功能。在標準PLL中,M和N值都是整數。Altera采用了delta-sigma調制器,并在反饋通路中使用了32位M和N值,支持反饋M分頻器采用分段值。這支持實現精確的頻率合成功能。能夠合成任意時鐘頻率,fPLL可以替代電路板上的振蕩器,從而降低了電路板成本,減小了電路板面積。

智能引腳布局提高了可布線能力,縮短了調試時間

Cyclone V FPGA以最低的開發成本提供最好的信號完整性。采用了常規棋盤式電源和地模式,簡化了布板。此外,器件左側是常規的收發器布局,并進行重復,而接收器總是在外部,從而實現了最佳信號完整性。還盡量遠離收發器放置存儲器I/O引腳,相對于收發器進行屏蔽。Altera的方法是,首先通過避免引腳布局問題,減少在耗時的調試過程上的投入。

評論