FPGA在電梯控制系統中的應用

摘 要: 介紹了基于Altera公司EP1K30TC144芯片的電梯控制器設計過程,描述了該控制系統的功能。該設計采用VHDL語言進行編程,以QUARTUSⅡ軟件為開發平臺,對本設計進行了仿真,并使用JTAG將程序代碼下載到實驗板上進行了硬件驗證。

本文引用地址:http://cqxgywz.com/article/138505.htm關鍵詞: 電梯控制器; VHDL; EP1K30TC144; QUARTUSⅡ

隨著社會的發展,電梯的使用越來越普遍,對電梯功能的要求也不斷提高,相應地其控制方式也在不斷發生變化。對于電梯的控制,傳統的方法是使用繼電器-接觸器控制系統進行控制,進入全微機化控制的時代,微型計算機在電梯控制上的應用日益廣泛。電梯的微機化控制主要有以下幾種形式:①PLC控制;②單板機控制;③單片機控制;④單微機控制;⑤多微機控制;⑥人工智能控制。隨著EDA技術的快速發展,CPLD/FPGA因其高速處理信號的能力、可在線編程、易于實現、開發周期短、便于維護等優點,使FPGA已廣泛應用于電子設計控制的各個方面。本文就是使用一片Altera公司的EP1K30TC144為控制中心,以VHDL編程語言為基礎進行了電梯控制器的設計,并做了仿真。

1 系統功能簡介

電梯控制器[1]的功能:每層電梯入口處設有上下請求開關;電梯內設有乘客到達層次的停站請求開關;電梯所處位置指示裝置及電梯運行模式指示裝置;電梯每分鐘升降一層樓。電梯到達有停站請求的樓層后,經過5 s電梯開門,開門指示燈亮,開門10 s后電梯門關閉,電梯繼續運行,直到運行完最后一個請求信號后停在當前層;能記憶電梯內外所有請求信號,并按照電梯運行規則依次響應,每個信號保留至執行后消除。

電梯運行規則:遵循方向優先的原則,電梯上升時,只響應比電梯所在位置高的上樓請求信號,由下到上逐個執行,直到最后一個上樓請求執行完畢,如更高層有請求下樓信號,則直接上升到有下樓請求的最高層,然后進入下樓狀態。電梯下降時,與上升狀態規則相反。

輸入信號定義:

系統復位信號:reset,高電平有效;

電梯入口處一層、二層的上樓請求開關:upone、uptwo;

電梯入口處二層、三層的下樓請求開關:downtwo、downthree;

電梯內部到達樓層的停站請求開關:one、two、three;

所有輸入信號的規定為:1表示有請求,0表示無請求;

輸出信號定義:

電梯外部上升和下降請求指示燈:lightup和lightdown,這些信號與upone、uptwo、downtwo和downthree信號相對應;

電梯內部乘客到達樓層的停站請求燈:arr,該信號與one、two和three相對應;

電梯所在樓層指示:p表示電梯在對應樓層;

電梯的運行狀態:lightdown指示向下運行,lightup向上運行,arr指示電梯的開關門狀態及是否到達樓層。

2 系統設計實現

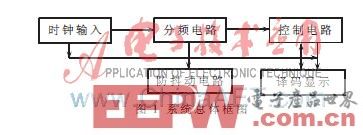

2.1 系統總體框圖

系統總體框圖如圖1所示。

2.2頂層電路的設計

縱觀各種基于FPGA的電梯控制器,很少有人介紹并使用構造體的結構描述方式。即在多層次的設計中,高層次的設計模塊調用低層次的設計模塊,或者直接使用門電路設計單元來完成一個復雜的邏輯電路的描述方法。結構描述方式最能提高設計效率,它可以將已有的設計成果方便地運用到新的設計中去。

本系統的頂層電路設計就采用構造體的結構描述方式。易于實現,易于糾錯,易于修改程序。

上層模塊源程序[4]及注釋:

library ieee;

use ieee.std_logic_1164.all;

entity total5 is

port(uo,ut,dt,dth:in std_logic--一、二、三層樓電梯外的上下樓請求鍵。

o,t,th:in std_logic;--一、二、三層電梯里的按鍵。

pres:in std_logic;--reset信號。

clk:in std_logic;--時鐘信號,1 MHz。

lightout:out std_logic_vector(6 downto 0);--數碼管的輸入信號。

lu,ld:out std_logic;--電梯上升,下降的燈。

arr:out std_logic);--開門的燈。

end;

architecture a of total5 is

signal templ0,templ2:std_logic;

signal templ1:integer range 3 to 1;

Signal

temp1,temp2,temp3,temp4,temp5,temp6,temp7:std_logic;

component bigmain--調用電梯控制模塊。

port(upone,uptwo,downtwo,downthree

:in std_logic;

one,two,three:in std_logic;

reset:in std_logic;

clk,clk2:in std_logic;

p:out integer range 3 to 1;

lightup,lightdown:out std_logic;

arrive:out std_logic);

end component;

component fangdou --調用防抖動模塊。

port(clk:in std_logic;

key:in std_logic;

keyout:out std_logic);

end component;

component fenpin--調用分頻器模塊。

port(clk:in std_logic;

clk1,clk2:out std_logic);

end component;

component display--調用譯碼顯示模塊。

port(clk :in std_logic;

light:in integer range 3 to 1;

segout:out std_logic_vector(6 downto 0));

end component;

begin

u1:fenpin port map(clk,templ0,templ2);

u4:fangdou port map(templ0,uo,temp1);

u5:fangdou port map(templ0,ut,temp2);

u6:fangdou port map(templ0,dt,temp3);

u7:fangdou port map(templ0,dth,temp4);

u8:fangdou port map(templ0,o,temp5);

u9:fangdou port map(templ0,t,temp6);

u10:fangdou port map(templ0,th,temp7);

u11:bigmain port map(temp1,temp2,temp3,

temp4,temp5,temp6,temp7,pres,clk,templ2,

templ1,lu,ld,arr);

u12:display port map(clk,templ1,lightout);

end;

2.3主模塊設計

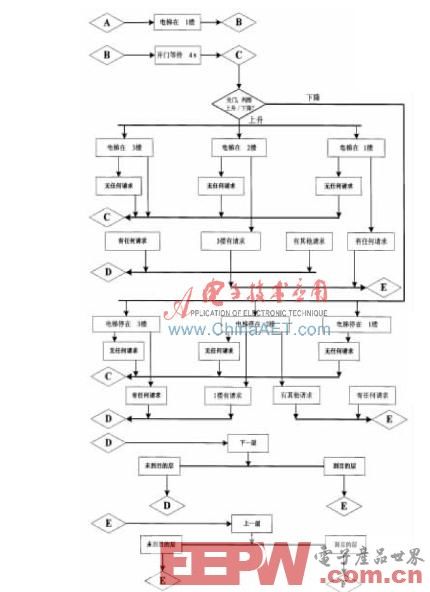

控制模塊是整個設計的核心部分,本設計采用狀態機[2]的方法來實現。依據電梯的功能要求,這里將電梯的工作分為10個狀態。狀態機如圖2所示。(1)控制模塊有兩個進程:k1控制輸入,無論電梯在什么狀態均能接收用戶的輸入請求,該進程由1 MHz的時鐘觸發;k2控制電梯的升、降、停留,該程序由1 Hz的時鐘觸發。(2)進程k1是由1MHz的時鐘作為觸發沿,不斷地檢測用戶是否有輸入請求,對于一、二、三層信號,分別有flag1、flag2、flag3和clear1、clear2、clear3兩套標志位來控制輸入請求是否有效,是否應該對標志位清零。程序有兩個表示電梯的狀態:一是位置狀態,二是運行狀態。

fpga相關文章:fpga是什么

分頻器相關文章:分頻器原理

評論