DSP與AD轉換器的接口電路設計

8 軟件設計

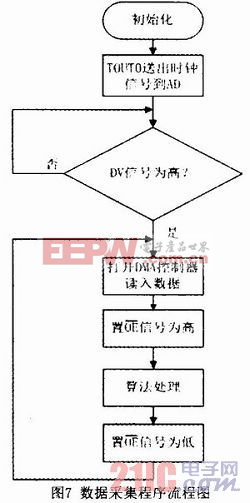

DSP控制數(shù)據(jù)采集的軟件程序流程如圖7所示。設置定時器參數(shù)提供TOUT0信號到ADS5422,ADS5422收到時鐘信號后開始采樣。由于高速AD特有的延遲特性,在收到采樣信號后,ADS5422至少需要在10個信號周期后才可以提供采樣數(shù)據(jù),所以設置好AD的時鐘后,讓ADS5422一直工作于采樣狀態(tài),通過控制ADS5422的引腳控制數(shù)據(jù)的輸出,當DSP檢測到DV信號為高后,打開DSP的DMA控制器讀入數(shù)據(jù),讀入一批數(shù)據(jù)后設置引腳為高,禁止數(shù)據(jù)輸出,DSP開始算法處理,并將處理后的結果輸出或者保存,然后設置引腳為低,ADS5422數(shù)據(jù)輸出,開始下一次數(shù)據(jù)處理。本文引用地址:http://cqxgywz.com/article/148831.htm

詳細的程序編寫流程如圖8所示。

評論