基于ADSP-TS201S的二維DMA數(shù)據(jù)傳輸

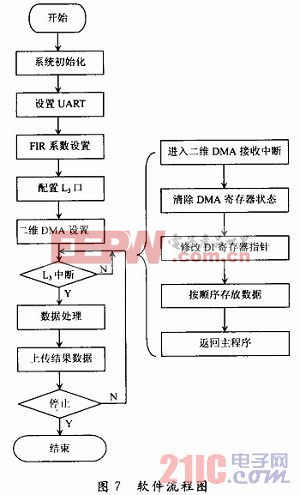

DSP0軟件需要完成L3鏈路口的初始配置和接受中斷函數(shù)的設(shè)計,首先進行DSP系統(tǒng)時鐘和UART及FIR濾波器系統(tǒng)的初始設(shè)置,然后進行二維DMA寄存器控制和內(nèi)存塊的分配,然后開啟硬件A/D采集,等待二維DMA中斷,進入中斷后獲得最終數(shù)據(jù)。軟件流程見圖7所示。本文引用地址:http://cqxgywz.com/article/149491.htm

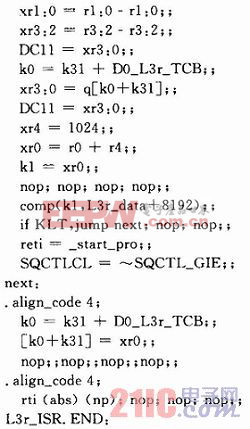

二維DMA中斷處理代碼如下:

其中的L3r_data為數(shù)據(jù)存儲區(qū)的首地址。

3 結(jié)語

本文介紹了TS201的二維DMA傳輸,結(jié)合實例說明了鏈路口二維DMA設(shè)置及應(yīng)用方法,給出軟件設(shè)置流程圖及關(guān)鍵代碼。實踐證明,二維DMA傳輸能夠保證大量數(shù)據(jù)的可靠傳輸,同時又解決了多處理器之間共用總線所產(chǎn)生的I/O瓶頸問題,增強了多處理器系統(tǒng)的并行處理能力,提高了系統(tǒng)流水線運行效率。

評論