基于FPGA的嵌入式PLC微處理器設計

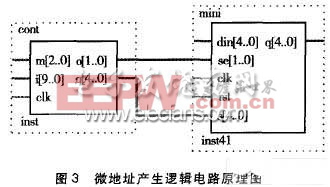

(3)微地址產生邏輯。微地址產生邏輯主要是根據微指令中的測試位及其他相關的條件來控制微地址的產生,它是根據一定的邏輯功能用VHDL語言編寫的,并且經過編譯和綜合后生成的模塊,如圖3所示。

其中,clk為同步時鐘信號,rst為復位信號,q為輸出的5位微地址值。其控制流程如下:

(1)系統啟動時,給出一個rst=1的復位信號,q端便輸出“00010”,為輸入掃描微程序的入口地址;(2)對應的微指令就從控存中輸出,然后該微指令中的5位下地址字段直接輸入到din端,3位測試位輸入到m端;(3)如果m=“000”,則q端輸出的地址值直接加1,且返回(2)繼續執行;否則,執行下一步;(4)如果m=“001”,則看i端輸入的用戶程序指令來判斷是否需要取數操作,如果需要,則q端輸出各個取數微程序的入口地址;如果不需要,則q端根據i的操作碼輸出相應指令的微程序入口地址,且返回(2)繼續執行;否則,執行下一步;(5)如果m=“010”,q端直接輸出din的地址值,且返回(2)繼續執行;否則,執行下一步;(6)如果m=“011”,則q端根據i的操作碼輸出相應指令的微程序人口地址,且返回(2)繼續執行。

2.2 運算器

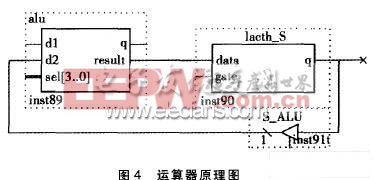

運算器是用來對輸入的數據進行算術和邏輯運算的部件 ,該ALU具有三輸入和兩輸出,d1和d2是參與邏輯運算的兩個位數據,其中dl來自外部的取數,d2來自輸出暫存器s,sel是指令的操作碼。result是運算后的結果,輸出后送給了暫存器S,q用來啟動定時器,如圖4所示。

2 3 RAM 圖4 運算器原理圖

RAM用來存儲用戶程序,它可以用FPGA中的LPM—RAM—DQ模塊來實現。其中,wren是讀寫控制端,當wren=0時為讀允許,這時在同步時鐘clock的上升到來時沿將address所對應的地址中的內容給輸出端q;當wren=1時為寫允許,這時在同步時鐘clock的上升沿到來時將data端的數據寫入到address所指明的地址中,如圖5所示。

評論