基于USB協議的DSP高速上位機接口設計

2.2 FPGA內的Linkport口邏輯設計

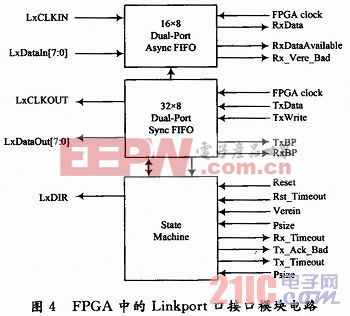

由于Link協議采用雙時鐘沿傳輸數據,而同步FPGA系統中,一般只采用單一時鐘的上升沿完成操作,因此需要將FPGA系統工作頻率SCLK設定為Link時鐘的2倍。然后將該時鐘的兩分頻輸出作為LxCLKOUT信號,有效數據則在SCLK的上升沿更新。

FPGA中的Linkport口接口模塊電路與ADSP-TS101的Linkport口完全兼容,且采用了雙向雙倍數據傳輸DDR技術,能實現雙向雙倍的數據傳輸。FPGA中的Link口接口模塊電路如圖4所示。本文引用地址:http://cqxgywz.com/article/150316.htm

圖5是FPGA內實現DSP數據上行的Linkport口接收時序仿真圖(基于Modelsim仿真軟件)。

Link口協議的一大特點就是在收發數據時可以選擇是否需要校驗位VERE比特,VERE的啟用或關閉可以通過ADSP-TS101中的寄存器來設置,也可以通過FPGA模塊中的Verein信號置高或置低來設置。該設計在FPGA中設置VERE信號的啟用或關閉。當VERE啟用后,FPGA模塊中的輸出信號Rx_Vere_Bad用于表征最后接收的128 b數據是否正確。由于使用VERE有兩個好處,一是能保證數據的完整性;二是能減小在兩個時鐘不嚴格一致的系統中傳輸數據時產生數據重疊的可能性。因而在設計中采用了帶數據校驗的傳輸方式。

評論